# Differential Power Processing Submodule Integrated Converters for Photovoltaic

**Power Systems**

by

Beomseok Choi

B.S., Kyunghee University, Yong-in, Rep. of Korea, 2006M.S., Kyunghee University, Yong-in, Rep. of Korea, 2009

A thesis submitted to the Faculty of the Graduate School of the University of Colorado in partial fulfillment of the requirements for the degree of Doctor of Philosophy Department of Electrical, Computer and Energy Engineering 2015 This thesis entitled: Differential Power Processing Submodule Integrated Converters for Photovoltaic Power Systems written by Beomseok Choi has been approved for the Department of Electrical, Computer and Energy Engineering

Dragan Maksimović

Prof. Khurram K. Afridi

Date \_\_\_\_\_

The final copy of this thesis has been examined by the signatories, and we find that both the content and the form meet acceptable presentation standards of scholarly work in the above mentioned discipline. Choi, Beomseok (Ph.D., Electrical Engineering)

Differential Power Processing Submodule Integrated Converters for Photovoltaic Power Systems

Thesis directed by Prof. Dragan Maksimović

System efficiency of conventional photovoltaic (PV) systems is adversely affected by mismatches among series connected cells, submodules, and modules. Module-level power converters, often referred to as dc optimizers, mitigate mismatch related losses by performing maximum power point tracking (MPPT) locally, at the PV module level. However, dc optimizers must process all PV power and in the process they introduce insertion losses even when there are no mismatches. Differential power processing (DPP) architectures mitigate mismatch-related losses while processing only a fraction of the PV system rated power, and without insertion losses. This thesis is focused on the design, implementation and evaluation of submodule integrated converters (subMICs) in the isolated-port DPP architecture. Using a simple voltage balancing approach where voltage reference is set by the shared isolated port, the subMICs can be controlled autonomously in a distributed manner, without the need for a central controller or communication among units. A custom CMOS controller integrated circuit is developed, which demonstrates voltage-balancing control, power limiting, and protection features on prototype subMICs based on bidirectional flyback converters. A system prototype, including three subMICs, is placed in the junction box of a standard 72cell PV module, replacing conventional bypass diodes. Performance of the subMIC-enhanced PV module is evaluated through laboratory and outdoor field experiments. Experimental results show greater than 99% module-level efficiency under 25% mismatch, using subMICs rated at one third of the PV power. A performance/cost analysis is performed to select the optimum subMIC design for a given PV system, resulting in best energy-yield improvements at minimum incremental cost.

## Dedication

To all who has given me trust.

### Acknowledgements

I would like to start off thanking my advisor, Prof. Dragan Maksimović, for his guidance, support, and his encouragement throughout my study at the University of Colorado, Boulder. He has shown patience and trust in me while assisting me with technical advices that were practical and easy to develop upon.

Starting the study in power electronics would have been very difficult without the help from Dr. Sungwoo Moon and Dr. Carlos Olalla. I really appreciate their help at the beginning of my studies.

Work on the analog IC would not have been possible without help from Dr. Jeff Morroni of Texas Instruments. Not only has he supported the chip tape-outs, but has also given me generous opportunities, goals, and vision for my career. I greatly appreciate his help.

Also, I would like to thank Fenglong Lu, Daniel Clement and Dr. Chris Deline for their help and collaboration in the project sponsored by ARPA-E<sup>1</sup>. I would not be able to meet my goals without their help.

<sup>&</sup>lt;sup>1</sup> The information, data, or work presented herein was funded in part by the Advanced Research Projects Agency-Energy (ARPA-E), U.S. Department of Energy, an agency of the United States Government. under Award Number DE-AR0000216. Neither the United States Government nor any agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

I would also like to express my thanks to my committee members: Prof. Robert Erickson, Prof. Khurram Afridi, Dr. David Jones, Dr. Chris Deline (NREL) and Dr. Dan Seltzer.

My deepest appreciation goes to all my CoPEC friends who have been going together in the same paths. The journey has been great with them in the lab. I would also like to wish the best to everyone.

Finally, I would like to thank my family for all their patience, support, love, and trust over the years. I could have not gotten here without them. I would like to give special thanks to my wife, Hanbyeol and my son, Jungwoo for understanding and trusting me.

## Contents

### Chapter

| 1        | Intro | oductio | n                                                | 1  |

|----------|-------|---------|--------------------------------------------------|----|

|          | 1.1   | Photo   | voltaic (PV) Systems                             | 3  |

|          |       | 1.1.1   | Photovoltaic (PV) Cells                          | 4  |

|          |       | 1.1.2   | Conventional PV Systems                          | 5  |

|          | 1.2   | Modu    | le Level Power Electronics                       | 8  |

|          | 1.3   | Differe | ential Power Processing (DPP) for PV Systems     | 10 |

|          | 1.4   | Thesis  | Objectives and Organization                      | 12 |

| <b>2</b> | Isola | ated-po | rt DPP Submodule Integrated Converter (subMIC)   | 14 |

|          | 2.1   | Archit  | sectures and Control Schemes                     | 14 |

|          |       | 2.1.1   | Optimal Control                                  | 14 |

|          |       | 2.1.2   | Sub-optimal Control                              | 16 |

|          |       | 2.1.3   | Voltage Balancing Control                        | 18 |

|          | 2.2   | Voltag  | ge Balancing with Bi-directional Flybacks in DCM | 20 |

| 3        | Desi  | ign Rea | lization of SubMICs                              | 22 |

|          | 3.1   | Power   | Stage                                            | 22 |

|          | 3.2   | Loss N  | Modeling                                         | 24 |

|          |       | 3.2.1   | Conduction Loss                                  | 24 |

|          |      | 3.2.2   | Switching Loss                                       | 25       |

|----------|------|---------|------------------------------------------------------|----------|

|          |      | 3.2.3   | Magnetics Loss                                       | 26       |

|          | 3.3  | Planar  | Magnetics                                            | 27       |

|          |      | 3.3.1   | Core Selections                                      | 28       |

|          |      | 3.3.2   | Winding Selections                                   | 30       |

|          |      | 3.3.3   | Loss Estimations                                     | 32       |

|          |      | 3.3.4   | Realization                                          | 37       |

|          | 3.4  | SubMI   | IC Controller IC                                     | 39       |

|          |      | 3.4.1   | Modes of Control                                     | 39       |

|          |      | 3.4.2   | Controller Blocks                                    | 43       |

|          |      | 3.4.3   | Realization                                          | 53       |

|          | 3.5  | Protot  | ype Board                                            | 56       |

| 4        | Subl | MIC Pe  | rformance Evaluation                                 | 58       |

| Т        | 4.1  |         | Stage Efficiency                                     | 58       |

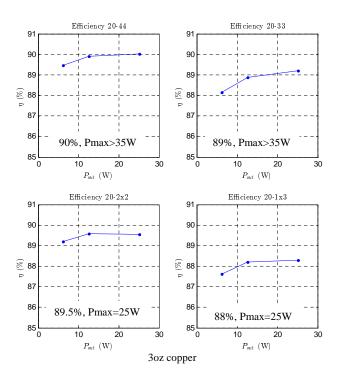

|          | 4.2  |         | ation of Magnetics Designs                           | 50<br>60 |

|          | 4.2  | 4.2.1   | Efficiency Measurements with Planar Magnetics        | 60       |

|          | 4.3  |         | bller IC Validation                                  | 64       |

|          | 4.0  |         |                                                      |          |

|          |      | 4.3.1   | Block Tests                                          | 65       |

|          |      | 4.3.2   | System Tests                                         | 68<br>70 |

|          |      | 4.3.3   | Quiescent Power Consumption                          | 70       |

| <b>5</b> | Syst | em Perf | formance Evaluation                                  | 72       |

|          | 5.1  | Bench   | Experiments                                          | 73       |

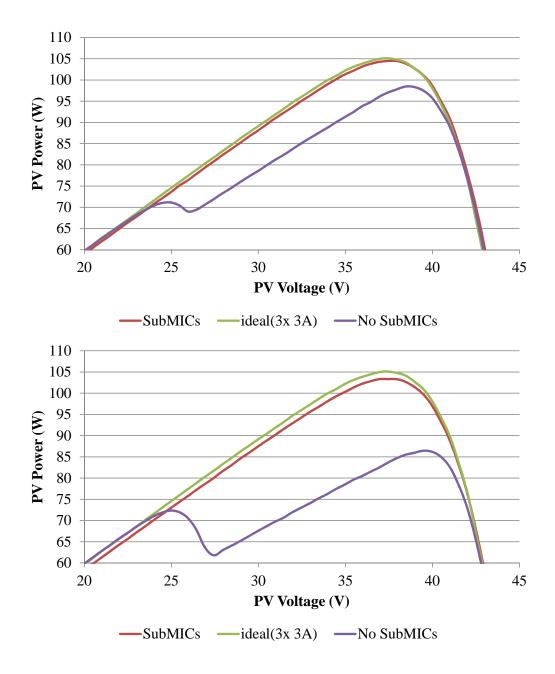

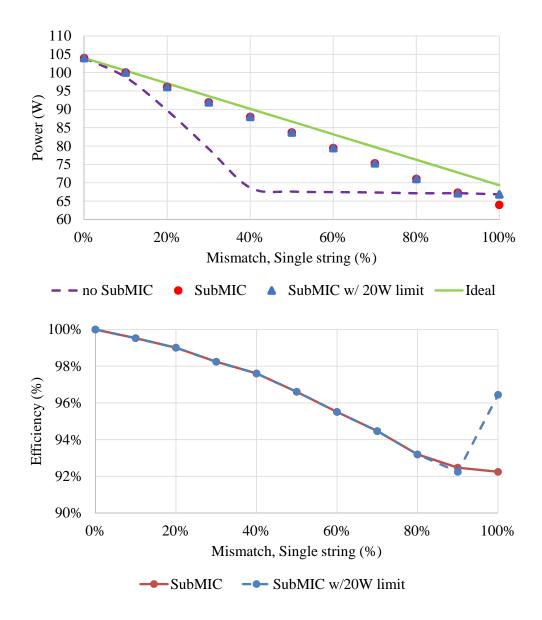

|          |      | 5.1.1   | Distributed Mismatch at Full Power Rated subMICs     | 74       |

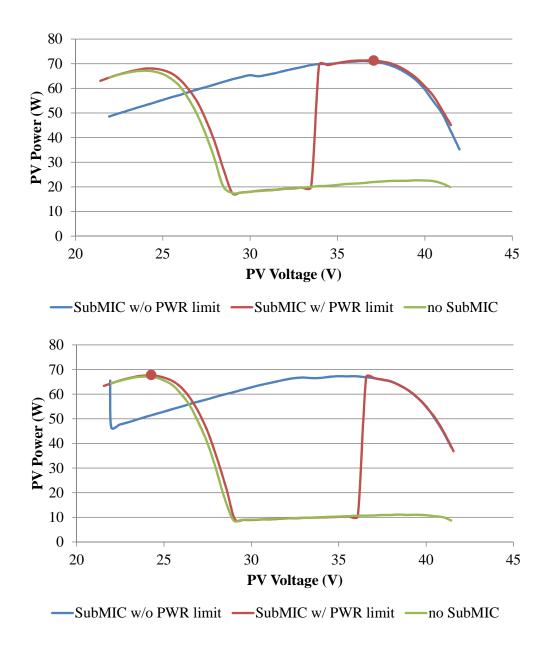

|          |      | 5.1.2   | Single Substring Mismatch with Power Limited SubMICs | 75       |

|          | 5.2  | Outdo   | or Experiments                                       | 79       |

|          |      | 5.2.1   | Substring Shading                                    | 80       |

|   |        | 5.2.2    | Partial Substring Shading                 | 85  |

|---|--------|----------|-------------------------------------------|-----|

|   | 5.3    | Analys   | sis of the Performance Testing Results    | 88  |

| 6 | Desi   | gn Opti  | mization of SubMICs for DPP PV Systems    | 89  |

|   | 6.1    | Cost N   | Indeling SubMICs based on Power Rating    | 90  |

|   | 6.2    | Reduce   | ed Cost SubMIC Designs                    | 92  |

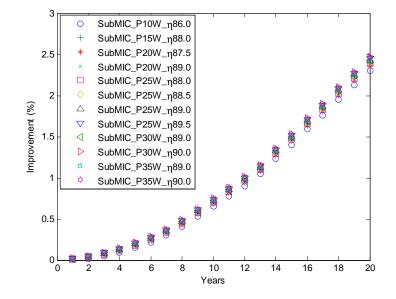

|   | 6.3    | Evalua   | ting System Performance of SubMIC Designs | 98  |

|   | 6.4    | System   | Performance Comparison Results            | 100 |

|   |        | 6.4.1    | Scenario 1: Ageing, 185W                  | 101 |

|   |        | 6.4.2    | Scenario 2: Ageing, 318W                  | 104 |

|   |        | 6.4.3    | Scenario 3: Shading, 208W                 | 106 |

|   |        | 6.4.4    | Scenario 4: Shading, 297W                 | 108 |

|   |        | 6.4.5    | Scenario 5: Shading, 189W                 | 111 |

|   | 6.5    | Result   | Analysis and Optimized Designs            | 113 |

|   |        | 6.5.1    | Ageing scenario analysis                  | 113 |

|   |        | 6.5.2    | Shading scenario analysis                 | 114 |

|   |        | 6.5.3    | Optimal designs based on SFOM             | 115 |

|   |        | 6.5.4    | Design distribution                       | 115 |

| 7 | Cone   | clusions |                                           | 120 |

|   | 7.1    | Future   | Work                                      | 124 |

|   |        |          |                                           |     |

| Е | Biblio | graphy   | 7                                         | 126 |

### Appendix

| A | Circuit Level Design of the SubMIC Controller | 131 |

|---|-----------------------------------------------|-----|

|   | 0                                             |     |

# List of Tables

### Table

| 3.1                                           | Design specifications                                                                 | 22                   |

|-----------------------------------------------|---------------------------------------------------------------------------------------|----------------------|

| 3.2                                           | Loss type classification for the DCM flyback                                          | 24                   |

| 3.3                                           | Specifications for TDK ELT type cores. Effective core area $A_e$ , length $l_e$ , and |                      |

|                                               | the inductance per wind estimation factor $A_L$ is shown                              | 29                   |

| 3.4                                           | Worst case flux density for the cores are given for several candidate turns.          |                      |

|                                               | Green denotes flux density is below $70\%$ of saturation and red denotes that         |                      |

|                                               | the core would saturate.                                                              | 29                   |

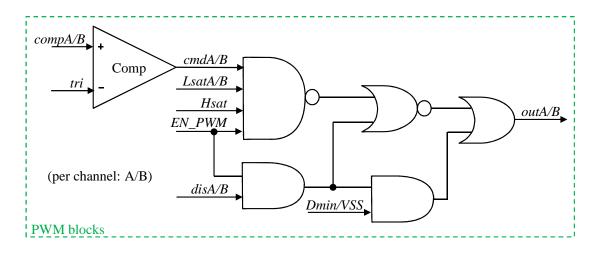

| 3.5                                           | Logic truth table of the combinational logic in $PWM\_blk$                            | 51                   |

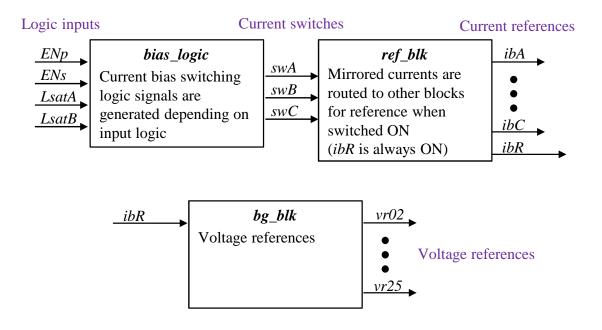

| 3.6                                           | Logic truth table of the combinational logic in $bias\_logic$ block and the cor-      |                      |

|                                               | responding affected blocks explained.                                                 | 53                   |

|                                               |                                                                                       | 00                   |

| 4.1                                           | Measured inductances.                                                                 | 60                   |

| 4.1<br>4.2                                    |                                                                                       |                      |

|                                               | Measured inductances                                                                  | 60                   |

| 4.2                                           | Measured inductances                                                                  | 60<br>71             |

| 4.2<br>5.1                                    | Measured inductances                                                                  | 60<br>71<br>74       |

| <ul><li>4.2</li><li>5.1</li><li>5.2</li></ul> | Measured inductances                                                                  | 60<br>71<br>74<br>75 |

| 6.1  | Estimated component costs                                  |

|------|------------------------------------------------------------|

| 6.2  | Magnetic core cost coefficients                            |

| 6.3  | PCB cost coefficients                                      |

| 6.4  | Prototype subMIC cost estimate                             |

| 6.5  | Magnetic specifications for different turns                |

| 6.6  | Efficiencies, power limits, and estimated costs of designs |

| 6.7  | Summary of PV system performance evaluation scenarios      |

| 6.8  | PV module specifications for scenario 1                    |

| 6.9  | PV module specifications for scenario 2                    |

| 6.10 | PV module specifications for scenario 3                    |

| 6.11 | PV module specifications for scenario 4                    |

| 6.12 | PV module specifications for scenario 5                    |

| 6.13 | Selected optimized subMIC designs and its specifications   |

# List of Figures

### Figure

| 1.1 | A typical PV system setup tied to the grid with an inverter                            | 3  |

|-----|----------------------------------------------------------------------------------------|----|

| 1.2 | PV cell models: simple<br>(left) and with parasitics included (right)                  | 4  |

| 1.3 | The IV curve (left) and PV curve of the first quadrant (right) of a PV cell            |    |

|     | shown for different insolation.                                                        | 5  |

| 1.4 | Structure of a PV module consisting of multiple substrings with PV cells in            |    |

|     | series. Typically, substrings have parallel by<br>pass diodes installed. $\ .\ .\ .$ . | 6  |

| 1.5 | A substring of PV cells with mismatch in cell 1(left) with its corresponding           |    |

|     | IV curve (top right), and the IV curve with by<br>pass diodes at a module level $% IV$ |    |

|     | (bottom right).                                                                        | 7  |

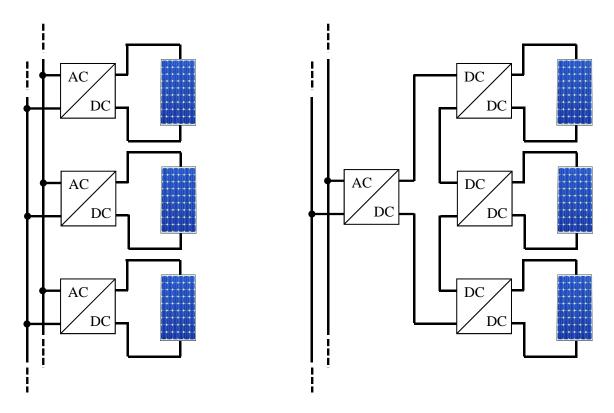

| 1.6 | Micro inverter PV system (left) and the DC optimizer PV system (right).                | 8  |

| 1.7 | Power balancing in a DPP PV system (left) and the corresponding operating              |    |

|     | points shown(right).                                                                   | 10 |

| 1.8 | Various DPP architectures: PV-to-PV shuffling (left), isolated PV-to-bus               |    |

|     | (center), and isolated port PV-to-bus (right).                                         | 11 |

| 2.1 | Isolated PV-to-bus architecture.                                                       | 15 |

| 2.2 | Isolated port PV-to-bus architecture with the auxiliary bus isolated with its          |    |

|     | voltage independent of the PV bus.                                                     | 18 |

| 2.3  | IV (top) and PV (bottom) curve of PV substrings with $25\%$ power variations       |    |

|------|------------------------------------------------------------------------------------|----|

|      | showing identical tangent lines (dot-dash, dot) overlaid over the $V_{MPP}$ point. | 19 |

| 2.4  | Bi-directional flyback topology used for the subMIC power stage with MOS-          |    |

|      | FET switches.                                                                      | 20 |

| 3.1  | Bi-directional flyback topology with snubbers for a subMIC                         | 23 |

| 3.2  | TDK ELT type cores for the design and a POT core                                   | 29 |

| 3.3  | Diagram of core and winding structure with key design geometries shown.            | 31 |

| 3.4  | FEMM analysis results comparing interleaved (left column) and non-interleaved      |    |

|      | (right column) AC copper loss when excited with a 4 A, 100 kHz sinusoidal          |    |

|      | current in the primary side winding (top row) and secondary side (bottom           |    |

|      | row). Magenta indicates higher current densities and cyan indicates the low-       |    |

|      | est current densities.                                                             | 32 |

| 3.5  | FEMM analysis results comparing AC loss dependent on the distance from             |    |

|      | the airgaps while the bottom winding is excited with current                       | 33 |

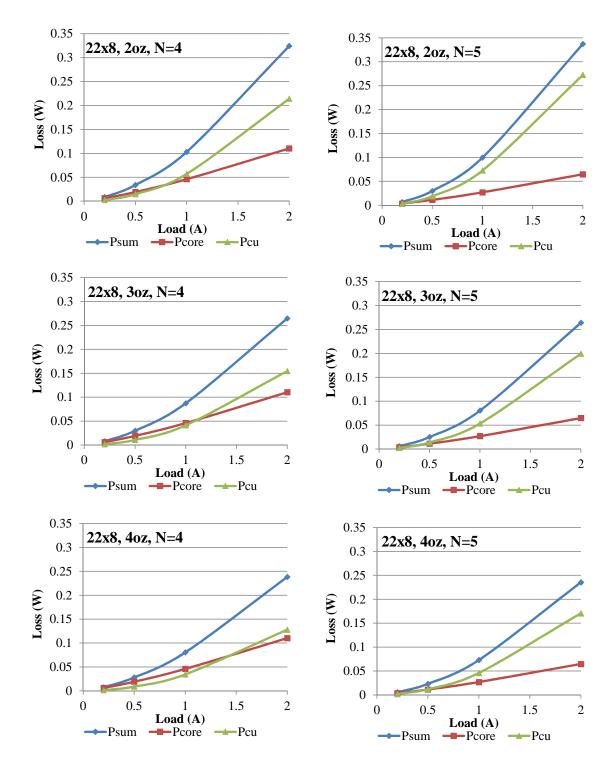

| 3.6  | Loss estimation for the planar magnetic designs using ELT20x7                      | 35 |

| 3.7  | Loss estimation for the planar magnetic designs using ELT22x8                      | 36 |

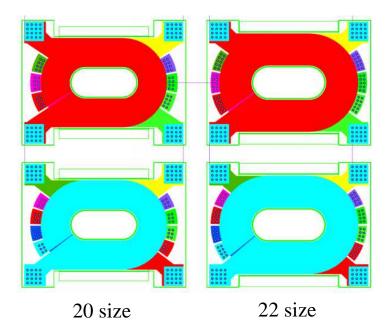

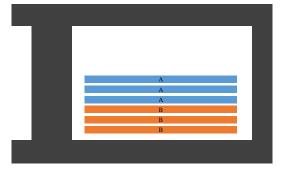

| 3.8  | Planar windings stack configurations.                                              | 37 |

| 3.9  | Planar PCB layout.                                                                 | 38 |

| 3.10 | Planar magnetics designed for the subMICs                                          | 39 |

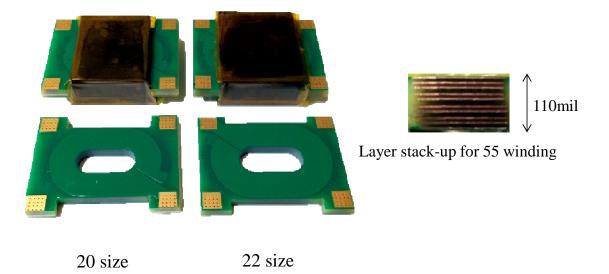

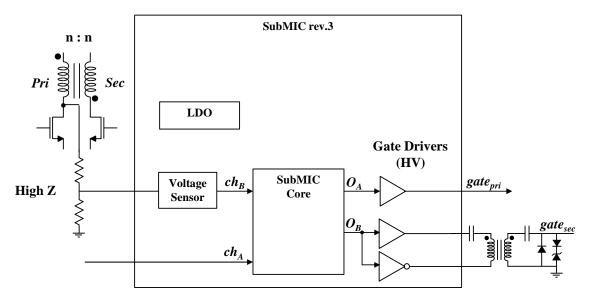

| 3.11 | Structure of the subMIC prototype with the controller IC                           | 40 |

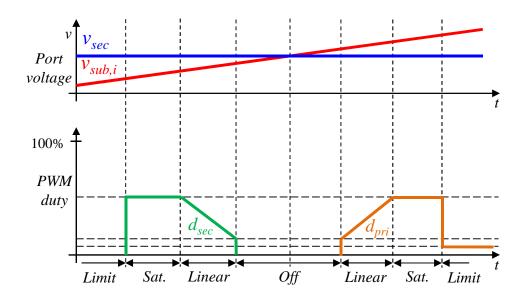

| 3.12 | Output duty cycles with input voltage difference evolving over time                | 41 |

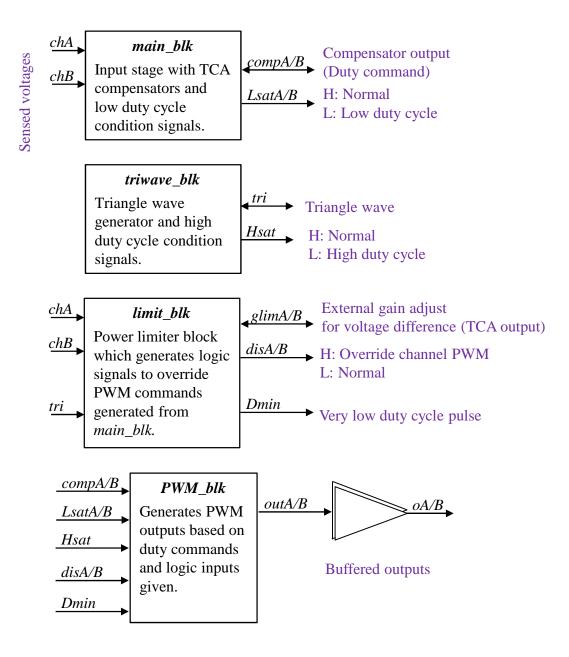

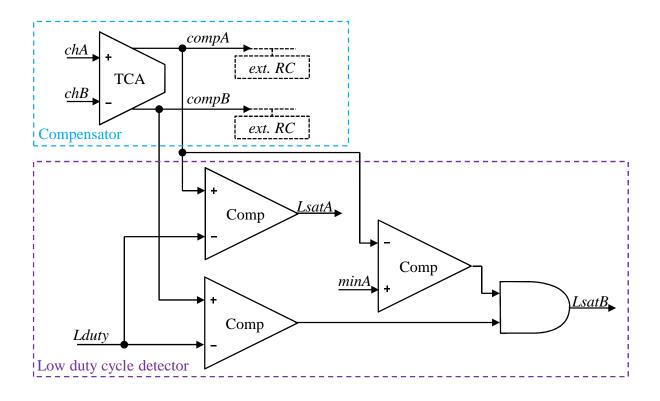

| 3.13 | Structure of the primary side function blocks.                                     | 45 |

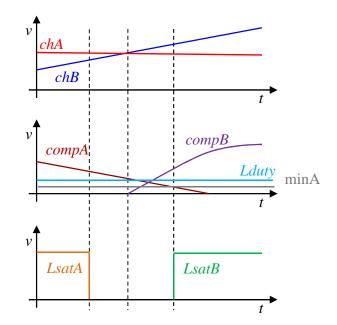

| 3.14 | Structure of the main_blk.                                                         | 46 |

| 3.15 | Signal relationship of the $main\_blk$ with changing port voltages                 | 47 |

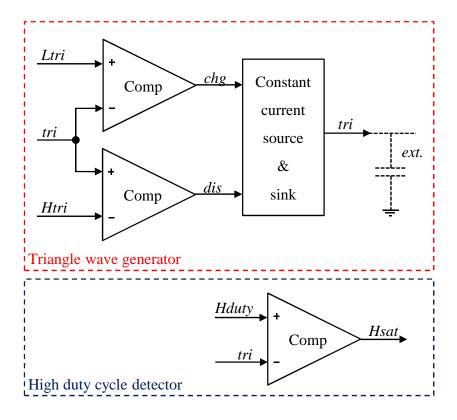

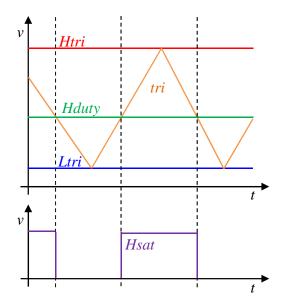

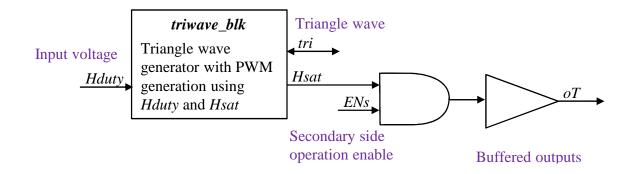

| 3.16 | Structure of the <i>triwave_blk</i>                                                | 48 |

| 3.17 | Signal relationship of the $triwave_blk$ with changing port voltages               | 48 |

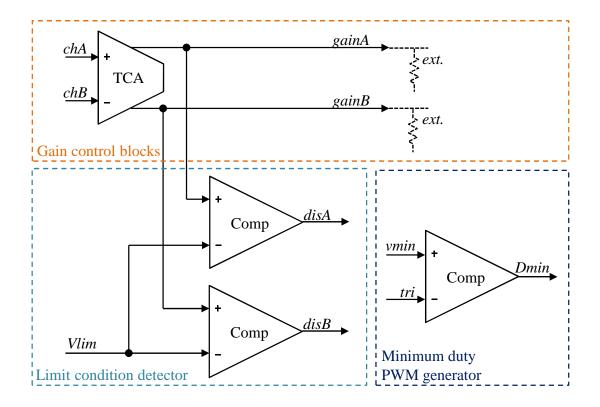

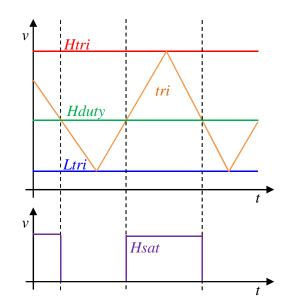

| 3.18 | Structure of the $limit_blk$                                                       | 49 |

|------|------------------------------------------------------------------------------------|----|

| 3.19 | Signal relationship of the $limit_blk$ with changing port voltages                 | 50 |

| 3.20 | Structure of the $PWM\_blk$                                                        | 50 |

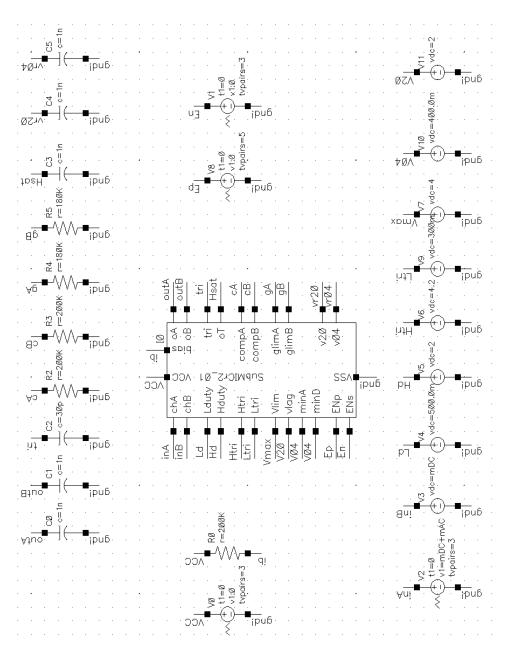

| 3.21 | Structure of the secondary side function blocks.                                   | 51 |

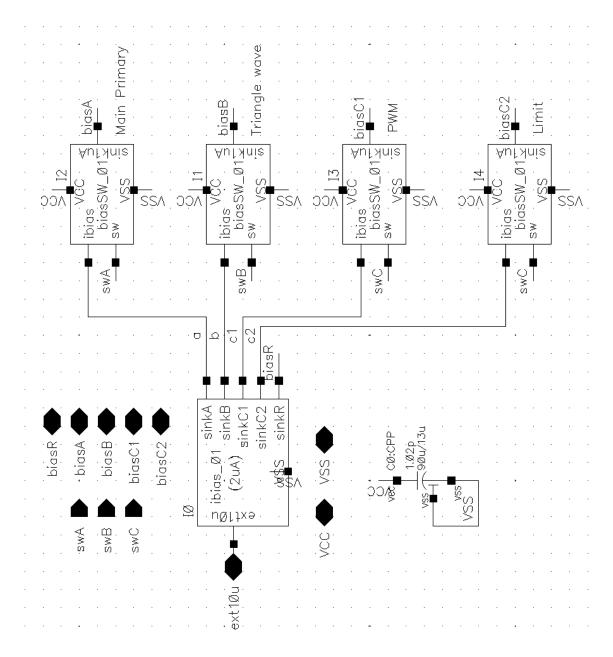

| 3.22 | Structure of the power save and reference function blocks                          | 52 |

| 3.23 | SubMIC controller IC packaged                                                      | 53 |

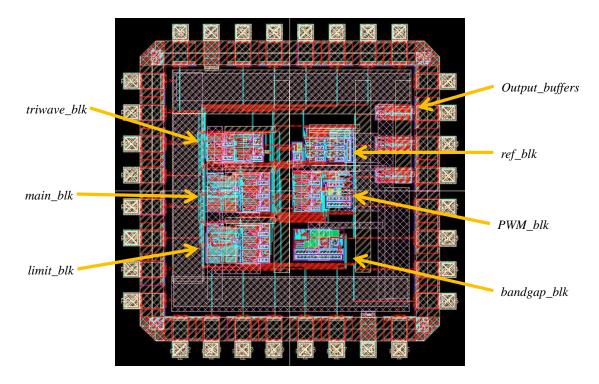

| 3.24 | IC layout.                                                                         | 54 |

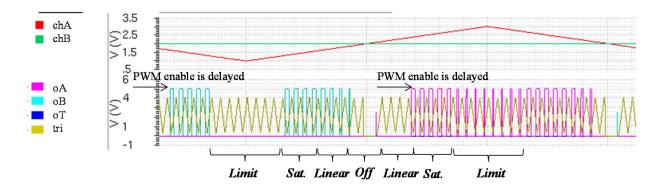

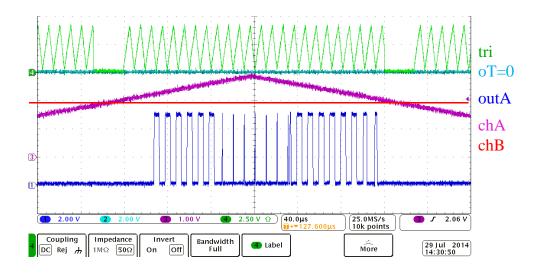

| 3.25 | Post layout simulation validating the modes of control for primary operation.      |    |

|      | Top row shows the input voltage signals varying with time. Bottom row shows        |    |

|      | the triangle wave overlaid over the two PWM outputs.                               | 54 |

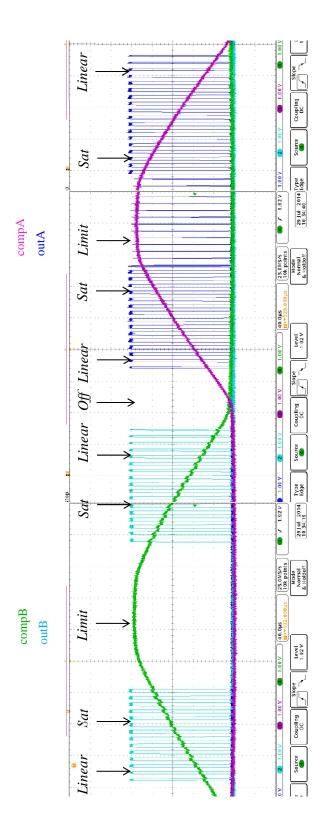

| 3.26 | Post layout simulation validating the modes of control for secondary operation.    |    |

|      | Top row shows the transition from primary to secondary operation. Bottom           |    |

|      | row shows which set of blocks are on in each mode                                  | 55 |

| 3.27 | Prototype subMIC board with three subMICs                                          | 57 |

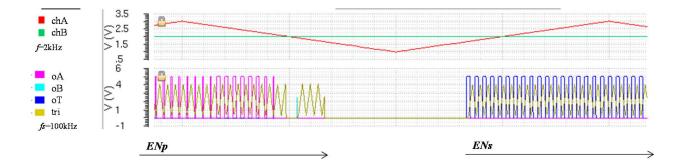

| 4.1  | Measured subMIC power stage efficiency with the 22-442 magnetics (top) and         |    |

|      | the 20-442 (bottom)                                                                | 59 |

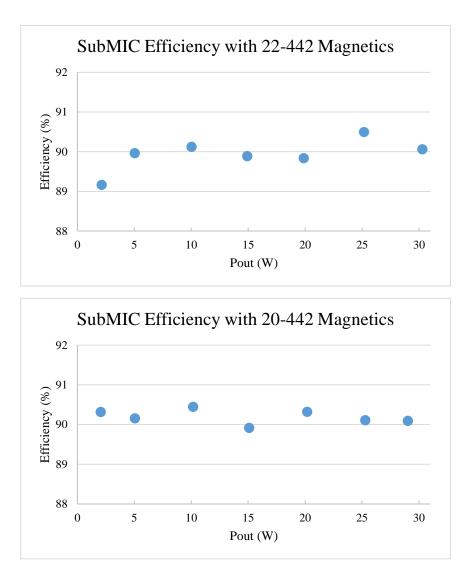

| 4.2  | Converter efficiency comparison for different magnetics designs                    | 61 |

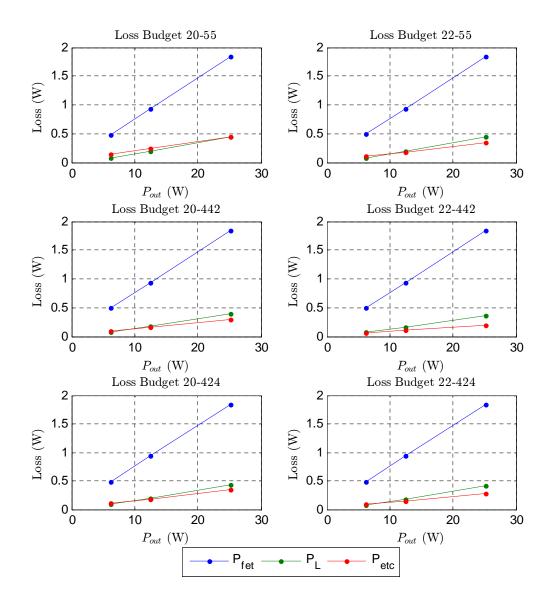

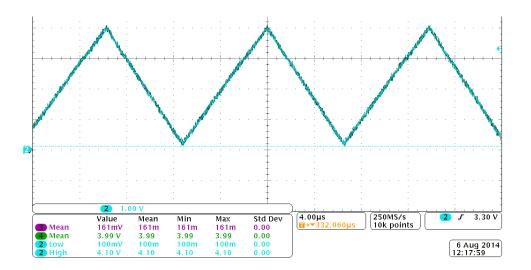

| 4.3  | Converter loss budget from the estimated losses where loss occurring on the        |    |

|      | MOSFET $(P_{fet})$ , the inductor $(P_L)$ , and other losses $(P_{etc})$ are shown | 62 |

| 4.4  | Magnetics loss budget from the estimated losses                                    | 64 |

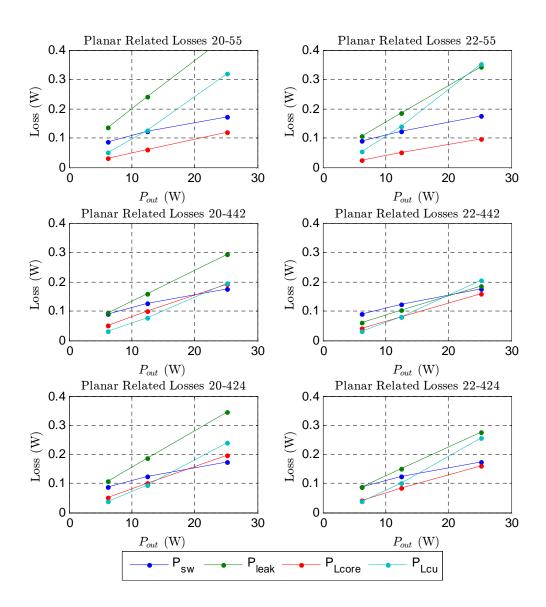

| 4.5  | Converter efficiency (top) and AC copper loss estimate (bottom) compared           |    |

|      | with varying distance from the airgap.                                             | 65 |

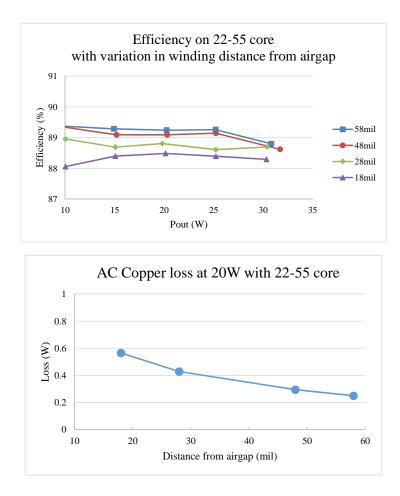

| 4.6  | SubMIC IC evaluation board.                                                        | 66 |

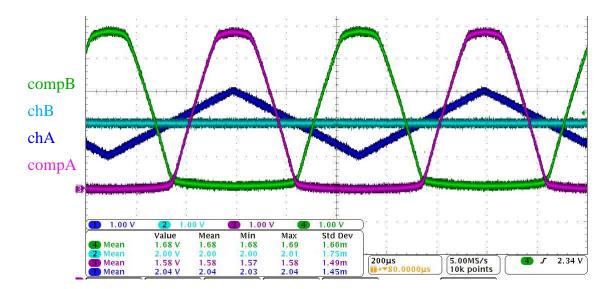

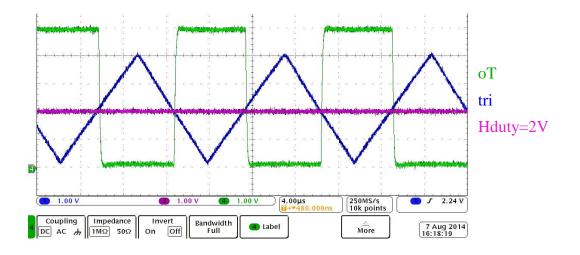

| 4.7  | SubMIC triangle wave.                                                              | 66 |

|      |                                                                                    | 00 |

| 4.8  | SubMIC TCA outputs.                                                                | 67 |

| 4.10 | Primary side operation verification.                                                                                | 69  |

|------|---------------------------------------------------------------------------------------------------------------------|-----|

| 4.11 | Secondary side operation verification                                                                               | 70  |

| 5.1  | Current biasing a PV substring.                                                                                     | 73  |

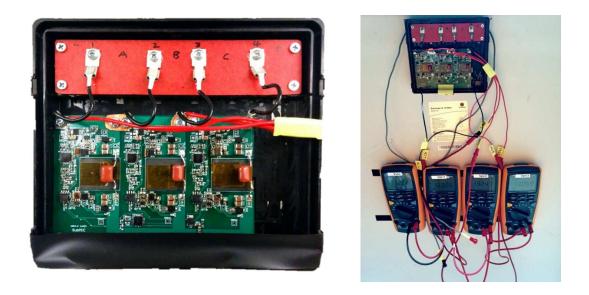

| 5.2  | Indoor experiment setup                                                                                             | 74  |

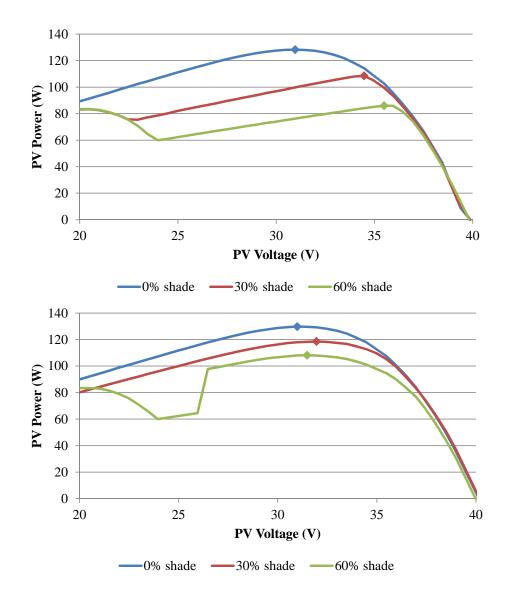

| 5.3  | $\rm PV$ sweep of distributed 25% mismatch (top) and 50% mismatch (bottom)                                          | 76  |

| 5.4  | $\rm PV$ sweep of power limited subMICs under $80\%$ mismatch (top) and $90\%$                                      |     |

|      | mismatch (bottom)                                                                                                   | 77  |

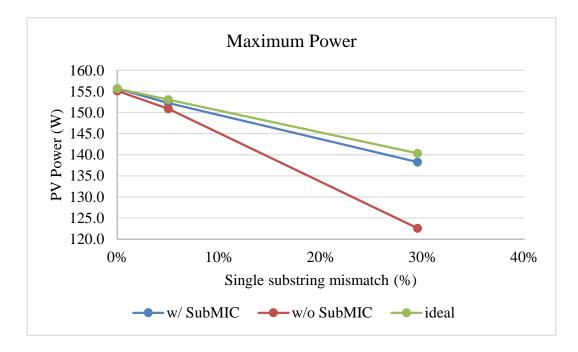

| 5.5  | Power (top) and efficiency (bottom) versus a single substring mismatch plots.                                       | 79  |

| 5.6  | SubMIC prototype placed inside the junction box of a 175 W PV module. $% \mathcal{A} = \mathcal{A} = \mathcal{A}$ . | 80  |

| 5.7  | Shading pattern for the fully shaded substring                                                                      | 81  |

| 5.8  | Power versus mismatch plot for the outdoor substring shading experiment                                             | 82  |

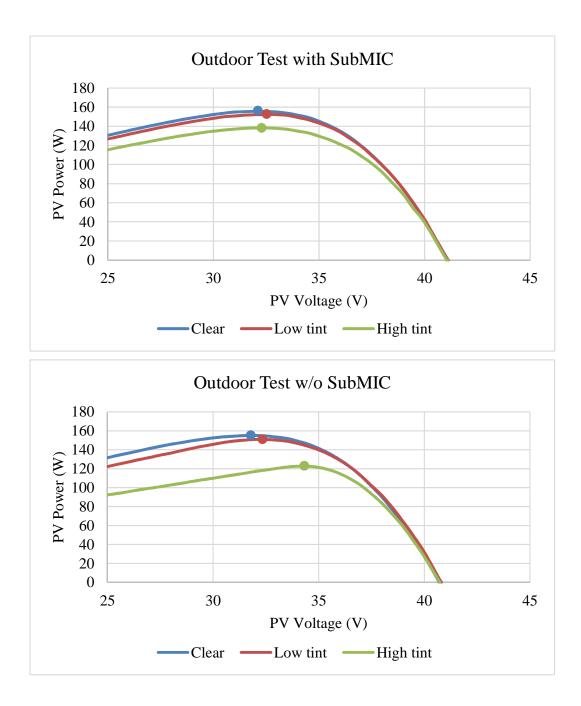

| 5.9  | PV curve of the conventional (bottom) and subMIC (top) system with sub-                                             |     |

|      | string shading                                                                                                      | 84  |

| 5.10 | Shading pattern for the partial shaded substring.                                                                   | 85  |

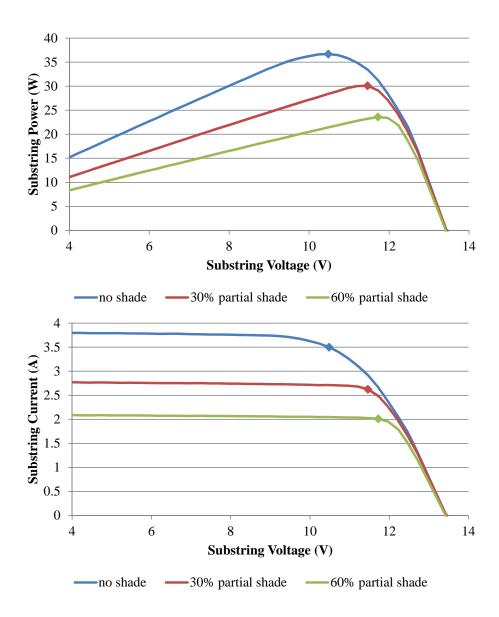

| 5.11 | $\mathrm{PV}$ (top) and IV (bottom) curve of a substring with partial shading                                       | 86  |

| 5.12 | PV curve of partial shading on a substring for a conventional (top) and power                                       |     |

|      | limited subMIC (bottom) system                                                                                      | 87  |

| 6.1  | Block diagram of improved subMIC IC design with the rev. 2 subMIC core                                              |     |

|      | reused                                                                                                              | 93  |

| 6.2  | Planar magnetic designs with different PCB layers and turns                                                         | 94  |

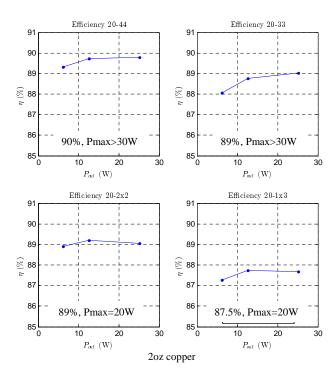

| 6.3  | Evaluated efficiencies for 3 oz copper planar magnetics design                                                      | 95  |

| 6.4  | Evaluated efficiencies for 2 oz copper planar magnetics design                                                      | 96  |

| 6.5  | Evaluated efficiencies for 1 oz copper planar magnetics design                                                      | 96  |

| 6.6  | Optimal design selection scenario.                                                                                  | 99  |

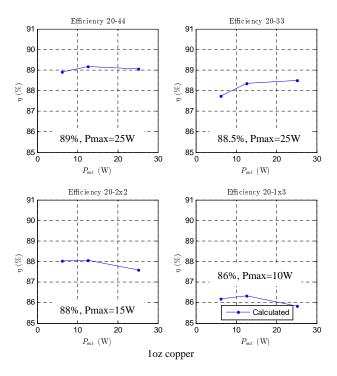

| 6.7  | Block diagram of optimal design selection.                                                                          | 101 |

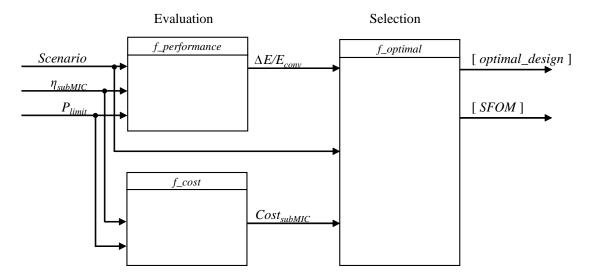

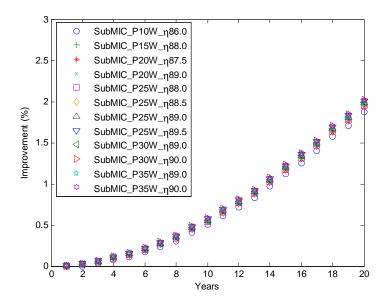

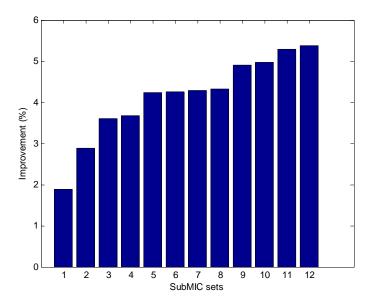

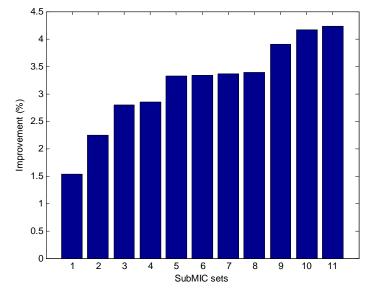

| 6.8  | System efficiency improvement from subMICs at a given year for scenario 1.                                          | 102 |

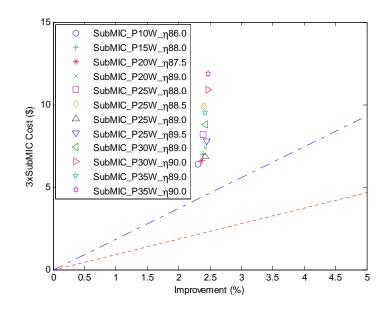

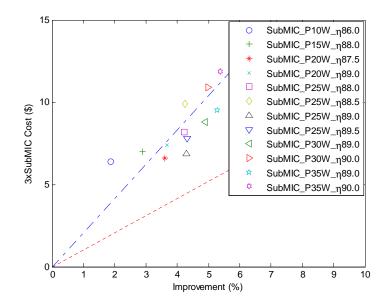

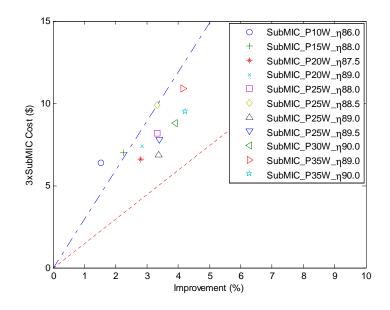

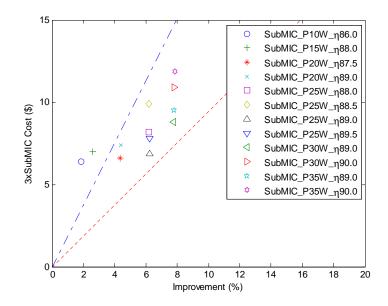

| 6.9  | SubMIC cost versus improvement plotted over PV module cost justification       |     |

|------|--------------------------------------------------------------------------------|-----|

|      | line at : $1/W(dot dash)$ and $0.5/W(dot)$ for scenario 1                      | 103 |

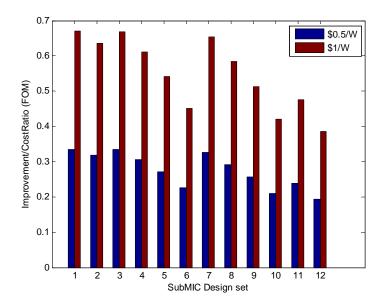

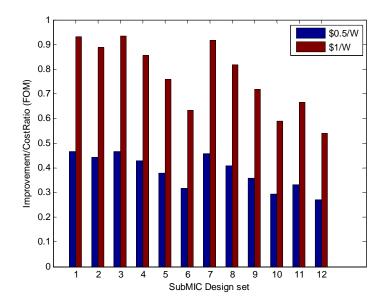

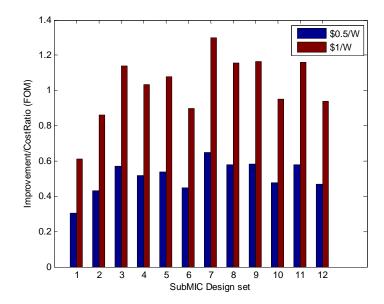

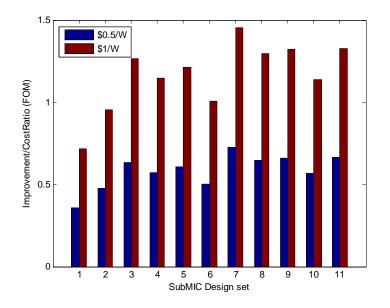

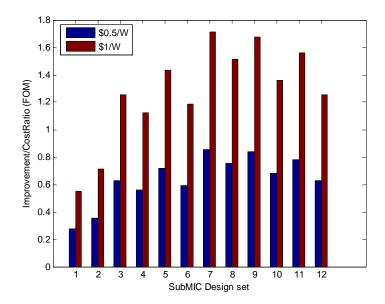

| 6.10 | Figure of merit comparison of designs at PV module cost of $0.5/W$ and $1/W$ , |     |

|      | where the first design set corresponds to the lowest power rated converter for |     |

|      | scenario 1                                                                     | 103 |

| 6.11 | System efficiency improvement from subMICs at a given year for scenario 2.     | 104 |

| 6.12 | SubMIC cost versus improvement plotted over PV module cost justification       |     |

|      | line at : $1/W(dot dash)$ and $0.5/W(dot)$ for scenario 2.                     | 105 |

| 6.13 | Figure of merit comparison of designs at PV module cost of $0.5/W$ and $1/W$ , |     |

|      | where the first design set corresponds to the lowest power rated converter for |     |

|      | scenario 2                                                                     | 105 |

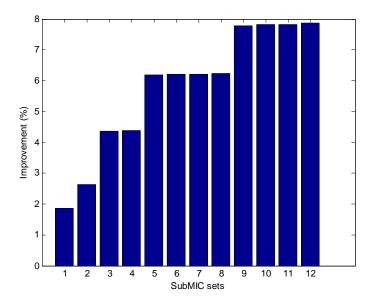

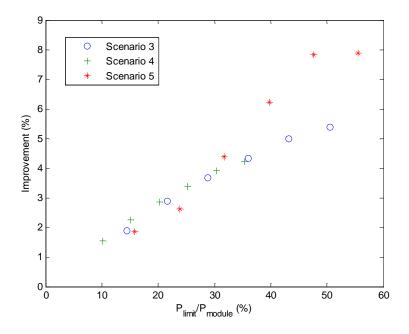

| 6.14 | System efficiency improvement from subMICs, where the first design set cor-    |     |

|      | responds to the lowest power rated converter for scenario $3$                  | 107 |

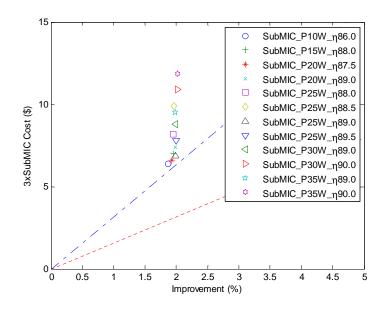

| 6.15 | SubMIC cost versus improvement plotted over PV module cost justification       |     |

|      | line at : $1/W(dot dash)$ and $0.5/W(dot)$ for scenario 3.                     | 107 |

| 6.16 | Figure of merit comparison of designs at PV module cost of $0.5/W$ and $1/W$ , |     |

|      | where the first design set corresponds to the lowest power rated converter for |     |

|      | scenario 3                                                                     | 108 |

| 6.17 | System efficiency improvement from subMICs, where the first design set cor-    |     |

|      | responds to the lowest power rated converter for scenario $4. \ldots . \ldots$ | 109 |

| 6.18 | SubMIC cost versus improvement plotted over PV module cost justification       |     |

|      | line at : $1/W(dot dash)$ and $0.5/W(dot)$ for scenario 4                      | 110 |

| 6.19 | Figure of merit comparison of designs at PV module cost of $0.5/W$ and $1/W,$  |     |

|      | where the first design set corresponds to the lowest power rated converter for |     |

|      | scenario 4                                                                     | 110 |

| 6.20 | System efficiency improvement from subMICs, where the first design set cor-    |     |

|      | responds to the lowest power rated converter for scenario $5$                  | 112 |

| 6.21 | SubMIC cost versus improvement plotted over PV module cost justification       |     |

|------|--------------------------------------------------------------------------------|-----|

|      | line at : $1/W(dot dash)$ and $0.5/W(dot)$ for scenario 5                      | 112 |

| 6.22 | Figure of merit comparison of designs at PV module cost of $0.5/W$ and $1/W$ , |     |

|      | where the first design set corresponds to the lowest power rated converter for |     |

|      | scenario 5                                                                     | 113 |

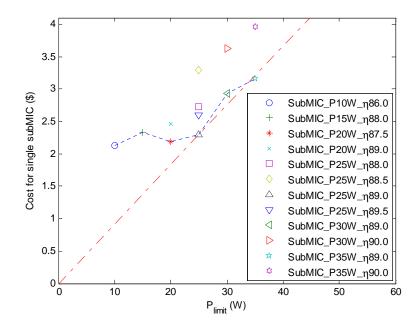

| 6.23 | Cost versus converter power rating with minimal cost designs shown for each    |     |

|      | power rating(dotted line) and a reference slope(dot-dash line) to compare      |     |

|      | other designs to the 25 W minimal cost design.                                 | 116 |

| 6.24 | Performance improvement versus subMIC power rating to module rating            | 117 |

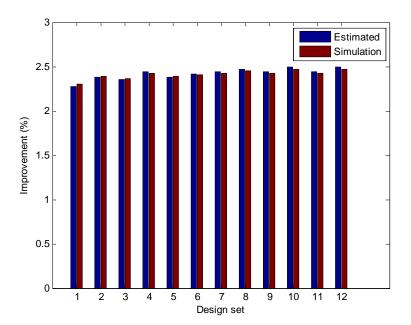

| 6.25 | Comparison of estimated and simulated system performance improvements          |     |

|      | for scenario 1                                                                 | 118 |

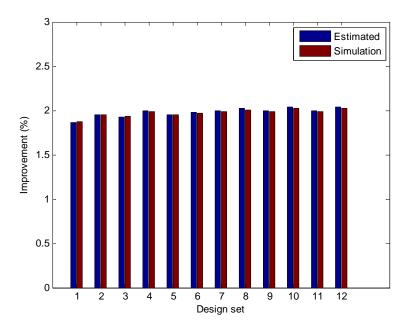

| 6.26 | Comparison of estimated and simulated system performance improvements          |     |

|      | for scenario 2                                                                 | 119 |

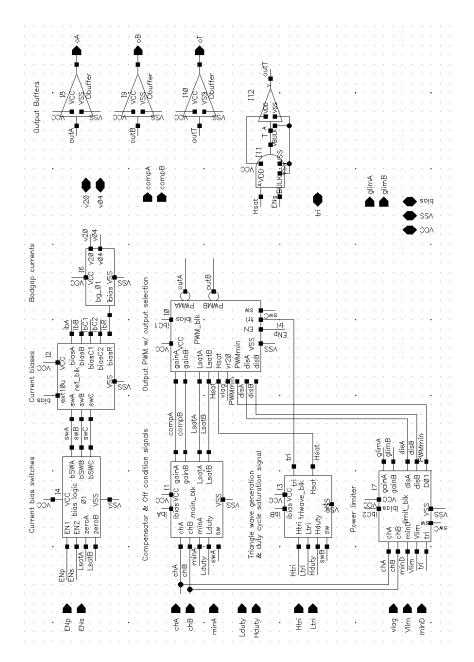

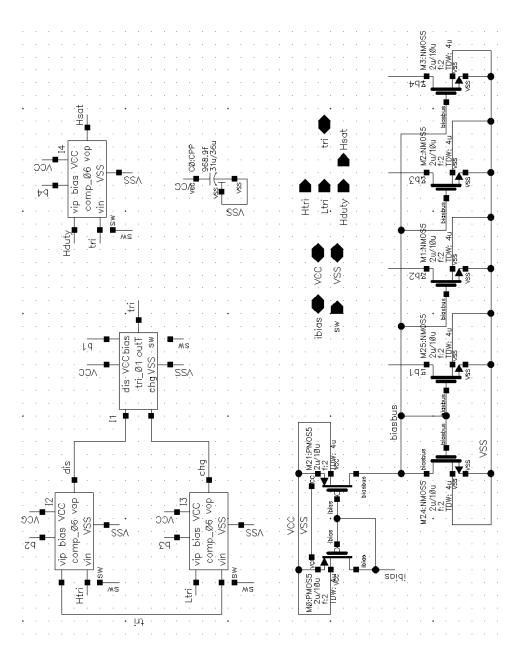

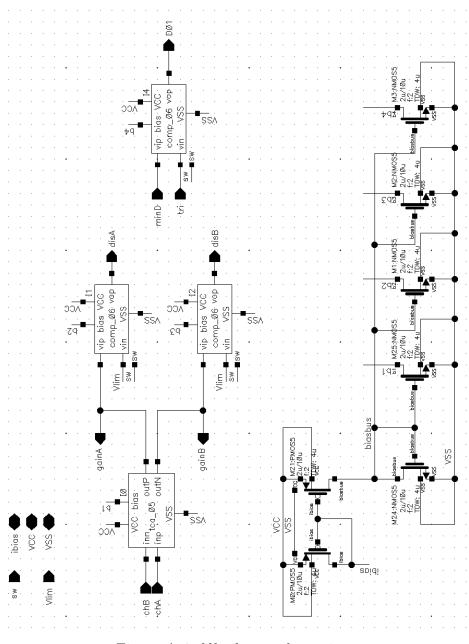

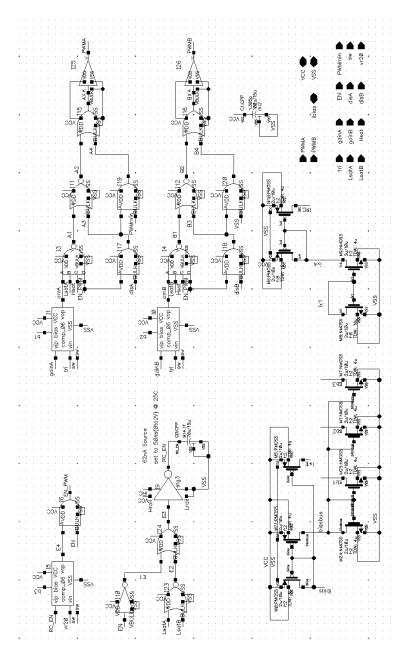

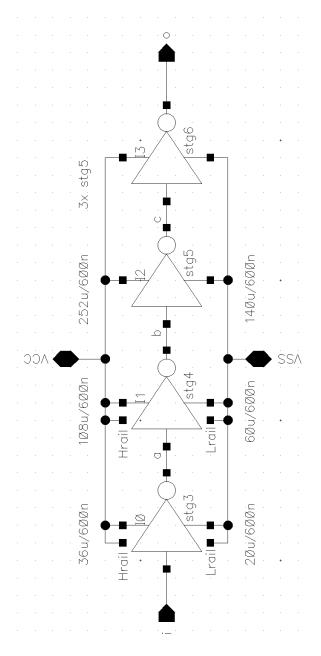

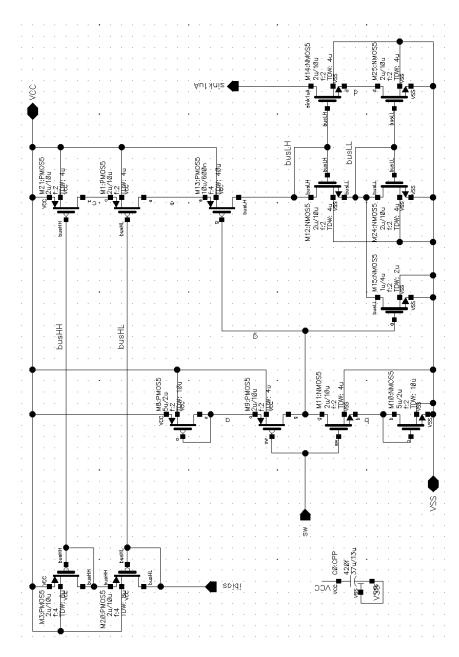

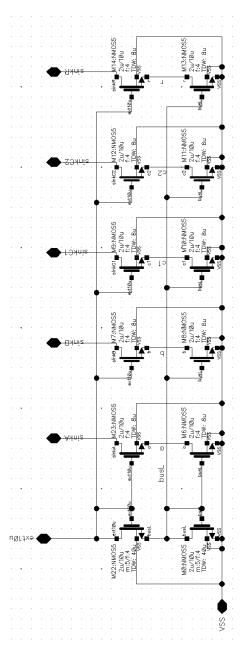

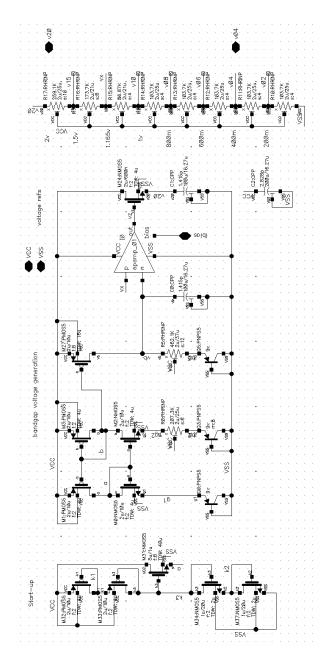

| A.1  | SubMIC schematic.                                                              | 132 |

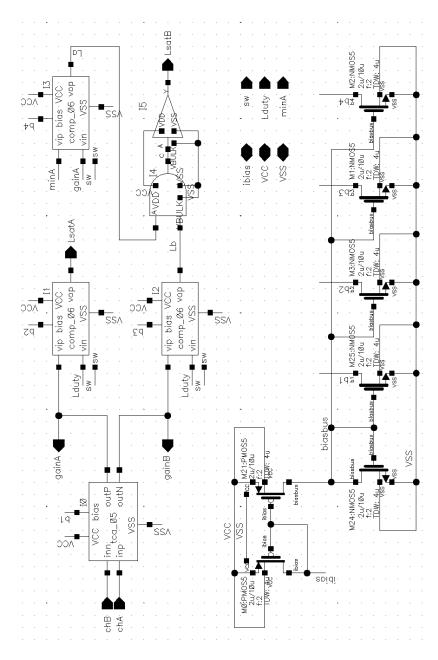

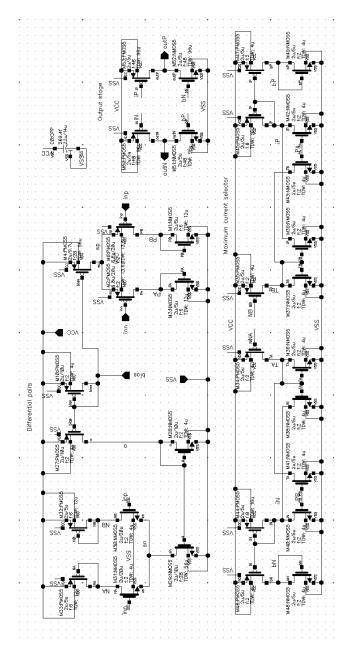

| A.2  | blks_main schematic.                                                           | 133 |

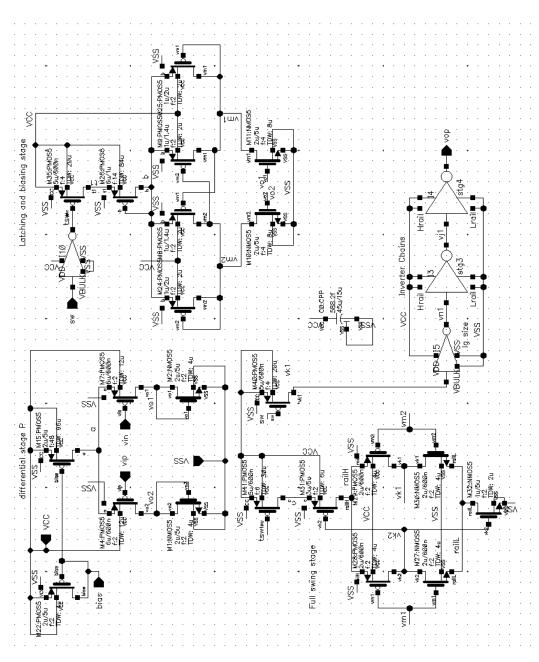

| A.3  | blks_triwave schematic.                                                        | 134 |

| A.4  | blks_limit schematic.                                                          | 135 |

| A.5  | $blks_PWM$ schematic                                                           | 136 |

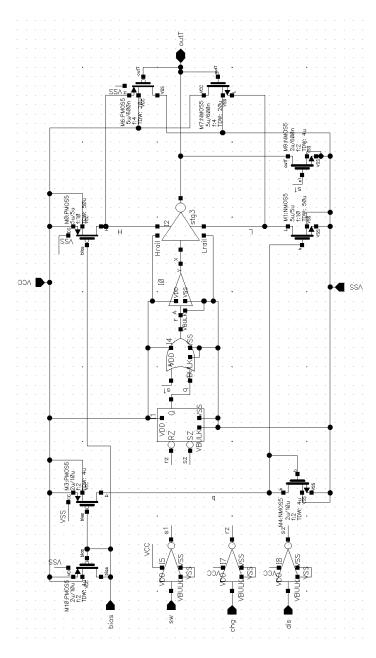

| A.6  | $blks\_ref$ schematic                                                          | 137 |

| A.7  | blks_oBuffer schematic.                                                        | 138 |

| A.8  | $mdl_tca$ schematic.                                                           | 139 |

| A.9  | $mdl_comp$ schematic.                                                          | 140 |

| A.10 | $mdl_tri$ schematic.                                                           | 141 |

| A.11 | $mdl_biasSW$ schematic.                                                        | 142 |

| A.12 | $mdl_{-ibias}$ schematic                                                       | 143 |

| A.13 | $mdl_bg$ schematic.                                                            | 144 |

| A.14 SubMIC test setup schematic. | <br>145 |

|-----------------------------------|---------|

# Chapter 1

### Introduction

With increasing focus on global environmental problems, interest in renewable and sustainable energy sources is increasing. Substantial growth can be observed in deployments of renewable energy sources, especially wind and solar. Power electronics is the technology that enables conversion of energy from these sources into electricity delivered to the ac power grid. Improving energy harvesting efficiency and reducing cost of renewable energy are the key goals in further developments of power electronics technology. In particular, solar photovoltaic (PV) systems are gaining popularity in residential, commercial and utility-scale systems due to the decreasing cost and increasing efficiency. of is gaining popularity as an energy source.

A single PV cell generates a very limited low dc voltage, which is not suitable for direct connection or conversion to the ac power grid. In practice, many PV cells are connected in series to obtain a higher dc voltage. Usually, a number, e.g. 60 or 72, of series connected PV cells are assembled into a PV module. PV modules are then connected in series to obtain even higher dc voltages. A dc-to-ac power electronics inverter is then used to converter dc power to ac power delivered to the ac power grid. The non-linear cell current-voltage (IV) characteristic results in the existence of a maximum power point (MPP). A task of the power electronics inverter is to operate the system at the MPP to maximize energy capture.

Due to the series connected nature of the PV cells, mismatches present in PV systems

degrade energy capture performance. Mismatches occur due to partial shading, temperature gradients across the system, tolerances in cell and module parameter, etc. Severe mismatches due to partial shading may cause reverse biasing of shaded PV cells, and "hot-spot" failures due to overheating. Conventional systems mitigate the problem by placing bypass diodes in parallel with substrings of PV cells within the PV module. In the presence of mismatches, the bypass diodes conduct, shorting out portions of the PV system, which results in reduced dc voltage, reduced output power, and losses in energy capture.

Various power electronics architectures have been investigated to address mismatchrelated losses. For example, distributed module-level dc-dc converters, known as dc optimizers can be used to perform maximum power point tracking (MPPT) at a finer granularity, thus mitigating energy capture losses related to mismatches. Dc optimizers, however, process full PV power, and introduce insertion losses, even when there are no mismatches in the system. Differential power processing (DPP) methods have been introduced more recently. In DPP approaches, distributed dc-dc converters can operate the PV modules or submodules at MPP while processing on the mismatch portion of power. Partially rated converters can be smaller and less expensive. Furthermore, there are no insertion losses in DPP architectures. Converters in DPP architectures can be applied at a finer granularity level, such as the submodule level, or even down at the cell level.

This dissertation is focused on the design and optimization of submodule integrated converters (subMICs) in the isolated-port DPP architecture [1–3]. Performance of subMIC prototypes is verified in both laboratory and outdoor experiments. Methods of reducing subMIC costs and selecting the optimal subMIC design for a PV system setup are also presented.

The thesis starts with an introduction, including an overview of typical conventional PV systems and technologies used to improve the PV system energy capture performance. The chapter concludes with a summary of the thesis goals and its organization.

#### 1.1 Photovoltaic (PV) Systems

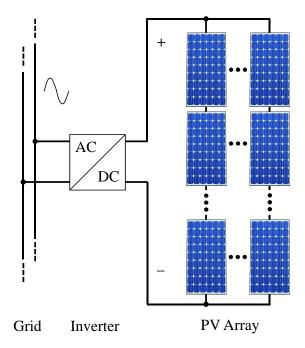

A typical PV system consists of many PV modules connected in series to obtain high DC voltages sufficient for AC grid connection via a power converter: an inverter. A PV system with an inverter connecting the system to the grid is shown in Figure 1.1.

Figure 1.1: A typical PV system setup tied to the grid with an inverter.

The inverter converts the DC power from the PV bus to AC power, It also makes sure the generated power output meets the grid regulation specifications. Also, on the DC bus side, PV voltage is controlled so that the system operates at MPP, hence maximizing the energy capture of the PV system. This is called maximum power point tracking (MPPT). Numerous literatures are available in this topic [4–6]. In order to understand why MPPT is required, the fundamental characteristics of a PV cell must be discussed.

#### 1.1.1 Photovoltaic (PV) Cells

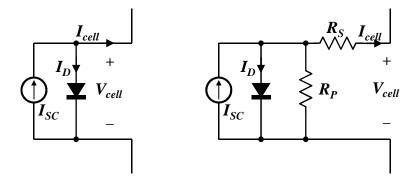

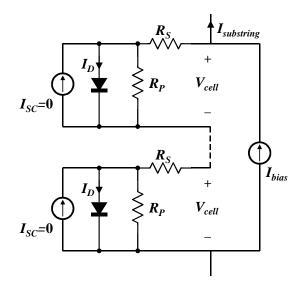

Most PV cells are semiconductor devices which act like a photo-sensitive diode. It can be modeled as in Figure 1.2 as a simple model or a model with parasitics [7].

Figure 1.2: PV cell models: simple(left) and with parasitics included (right).

When light radiation hits a cell (also called insolation), current flow  $(I_{SC})$  is generated and partial current  $(I_D)$  is flown through a diode. The diode current is dependent on the voltage across the diode. Then the VI characteristic of the PV cell can be found through the following:

$$I_{cell} = I_{SC} - I_D$$

=  $I_{SC} - I_0 \left( exp \left[ \frac{V_{cell}}{nV_T} \right] - 1 \right)$  (1.1)

If the parasitics associated with the cell  $(R_S, R_P)$  are included, then:

$$I_{cell} = I_{SC} - I_0 \left( exp \left[ \frac{V_{cell}}{nV_T} \right] - 1 \right) - \frac{V_{cell} + I_{cell}R_S}{R_P}$$

(1.2)

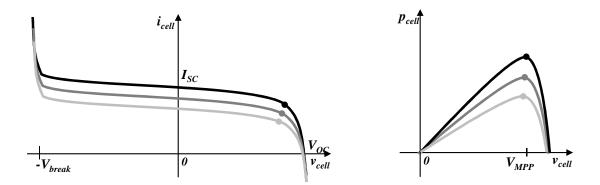

If the  $i_{cell}$  and  $v_{cell}$  are plotted for  $v_{cell}$ , the characteristic of the PV cell can be seen. Plots of the cells are shown for different insolation levels in Figure 1.3. The plots are called the IV and PV curves, respectively. As insolation increases, power increases. Note that the plot also show reverse breakdown characteristics at  $-V_{break}$ , which is not modeled in Figure 1.2.

The Y-axis crossing of the IV curve corresponds to  $I_{SC}$ , the short circuit current of the cell.  $I_{SC}$  scales with insolation. The X-axis crossing is defined as the open circuit

Figure 1.3: The IV curve (left) and PV curve of the first quadrant (right) of a PV cell shown for different insolation.

voltage,  $V_{OC}$ .  $V_{OC}$  depends strongly on temperature as  $V_T$  is a temperature dependent variable. Hence,  $V_{OC}$  decreases as temperature rises. Typically,  $V_{OC}$  is about 0.6 V for mono-crystalline silicon cells.

The second quadrant of the IV curve suggests that the PV cell can actually dissipate power even when insolation is present. Operating in this region can cause the cell to overheat and damaged in the worst case. Cells operating in this region are known to cause "hotspots" [8,9] due to the overheating. Therefore, it is critical to maintain positive  $v_{cell}$  to prevent operation in this region.

Also, the PV curve in Figure 1.3 shows that a peak power operating point exists. This is called the maximum power point (MPP) at  $V_{MPP}$ . It is desired to operate each PV cell at this operating point to maximize energy capture.

#### 1.1.2 Conventional PV Systems

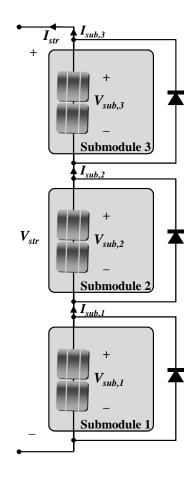

Voltage of a single PV cell does not supply enough voltage for efficient power conversion or utilization. Suitable voltage is obtained by connecting PV cells in series, hence conventional PV modules consists of series connected PV cells. A typical PV module structure is shown in Figure 1.4 with parallel bypass diodes.

Bypass diodes are connected in parallel to each PV substring to mitigate the negative

Figure 1.4: Structure of a PV module consisting of multiple substrings with PV cells in series. Typically, substrings have parallel bypass diodes installed.

effects of series connected PV cell. Series connected PV cells operate at a common string current  $(I_{str})$ . If mismatch in insolation, temperature, or cell characteristic exists, not all PV cell would operate at MPP. In the worst case, the PV cell could be dissipating power.

One PV cell with low insolation (*cell*, 1) is shown in the left of Figure 1.5 in a small substring. The IV curve shown on top right of Figure 1.5 shows the issue related to PV cell mismatch. While cell 2 and 3 can operate at MPP, cell 1 is shown to be dissipating power and causing a hotspot. The problem can be mitigated by placing bypass diodes in parallel to the cell. Then, the cell would not be operating at extreme reverse bias. Also, even if the cells are reverse biased, the power dissipation would occur mostly on the bypass diode.

Figure 1.5: A substring of PV cells with mismatch in cell 1(left) with its corresponding IV curve (top right), and the IV curve with bypass diodes at a module level (bottom right).

However, due to the cost, complexity and forward voltage drop of diodes, the bypass diodes are usually placed in parallel at the substring level. The bottom right IV curve of Figure 1.5 shows how the PV module operating points would be at the substring level. Notice that the negative voltage is now clamped to the bypass diode forward voltage drop  $(V_F)$ .

The conventional system with bypass diodes may prevent severe damage to the PV module while also mitigating severe degradation in energy capture efficiency. However, using bypass diodes are not the best approach and can be improved [10, 11].

Figure 1.6: Micro inverter PV system (left) and the DC optimizer PV system (right).

#### **1.2** Module Level Power Electronics

In conventional systems as in Figure 1.1, maximum power point tracking (MPPT) is performed at the central inverter to ensure operation at MPP. However, operating the PV bus at MPP does not guarantee that all the PV cells in the system will also operate at MPP. Mismatches in the PV modules and cells are likely to be present,hence not operating at MPP.

MPP at a finer granularity level can improve energy capture. PV Module level power electronics (MLPE) such as micro-inverters [12] and DC optimizers [13,14] perform MPP at the module level to operate each module at MPP. Also, power processing done at a much finer granularity level are investigated in [15,16]. The module level MPPT architectures are shown in Figure 1.6. Architectures are discussed assuming module level implementations. Both micro-inverters and DC optimizers enhance system level energy capture by ensuring MPPT at the modular level. The significant difference between the two architectures is that the micro-inverter does not require a large central inverter. On the other hand, the DC optimizer retains the same grid interfacing inverter and DC bus.

In a micro-inverter system, the power converters usually boosts the PV module voltage directly to the grid voltage. Also, the switches used in the converters would be rated at the grid voltage. Each micro-inverter power rating would be smaller than the conventional central inverter, but the voltage rating would be the same. The efficiency of power processing (via converters) in the system can be expected to be similar to the conventional central inverter case due to the identical voltage rating, but overall energy capture would be relatively better due to finer granularity MPPT.

As for the DC optimizer, the DC-DC converter outputs are connected in series. The sum of the output voltages determines the DC bus voltage to the central inverter. Unlike the micro-inverter, the voltage ratings scale down as more DC optimizers are connected in series. However, this architecture still requires the central inverter.

It is not directly clear which architecture is more cost effective or efficient. However, it can easily be seen that the added converters process all the power of the PV modules (full power processing). Given the efficiencies of the converters, the maximum energy obtainable from the system will have the following relationship:

$$E_{micro-inverter-system} \le \sum_{i=1}^{N} E_{PVmodule,i} \cdot \eta_{micro-inverter}$$

(1.3)

$$E_{DC-optimizer-system} \le \sum_{i=1}^{N} E_{PVmodule,i} \cdot \eta_{DC-optimizer} \eta_{inverter}$$

(1.4)

The full power processing architectures have energy capture efficiency limited by the converter efficiency at all times. More on the actual performances can be found in the previously referred literatures.

#### **1.3** Differential Power Processing (DPP) for PV Systems

The converters of architectures discussed in Section 1.2, process all of the energy captured from the PV modules. Going back to the fundamental problem of series connected PV cells, it can be noted that the problematic issues arise from the common current operating point. When mismatches among series connected cells exist, not all cells can operate at MPP. If the mismatched cells can be operated at different current operating points, all cells could operate at MPP. In order to operate each cell with independent current, the difference in current must be diverted through an auxiliary path as power. This method is commonly called differential power processing (DPP). Figure 1.7 show the simplified operation of the DPP PV system.

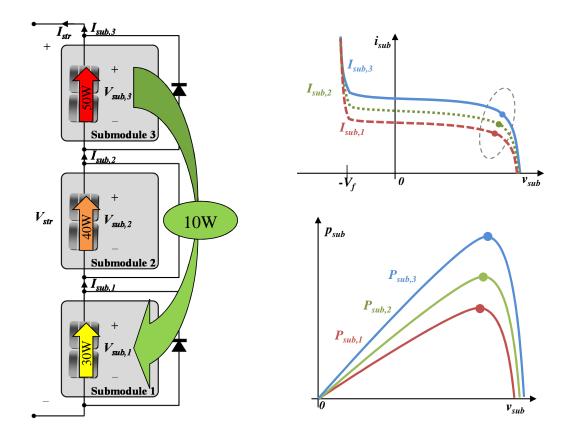

Figure 1.7: Power balancing in a DPP PV system (left) and the corresponding operating points shown(right).

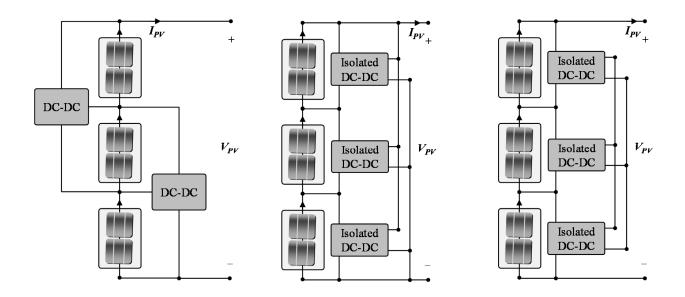

Numerous literature on DPP architectures with various architectures are proposed [1,17–20]. Among them, few architectures are shown in Figure 1.8: PV-to-PV shuffling [17], isolated PV-to-bus [18], and isolated port PV-to-bus [1]. Substring scale implementation is assumed in the figure.

Figure 1.8: Various DPP architectures: PV-to-PV shuffling (left), isolated PV-to-bus (center), and isolated port PV-to-bus (right).

The PV-to-PV shuffling architecture processes the mismatched power between adjacent substrings. However, it can still balance mismatched power for non-adjacent substrings. The architecture requires one less bi-directional converter than the number of substrings in series. In this architecture, the total power processed in the converters varies with the position of the mismatch, even when mismatched power is the same.

The isolated PV-to-bus architecture requires isolated bi-directional converters. While one side of the converter is connected to a dedicated substring, the other side of the converter is connected in parallel to other subMICs and the PV bus. This architecture requires isolated converters. Mismatched power is processed via the added bus. It is used to reroute power in and out from the substrings. If minimal power processing is desired, a central controller is required to determine the power processing scheme.

The isolated port PV-to-bus architecture is similar to the isolated PV-to-bus architecture, but does not have the auxiliary bus connected to the PV bus. Compared to the isolated PV-to-bus architecture, the minimum power processed can be sub-optimal due to the lack of power flow from the PV bus. However, the isolated bus is no longer required to be at PV bus voltage. The flexible axillary bus voltage allows the use of lower voltage rated devices.

Each architecture has its trade-offs regarding system performance improvement, size, and costs. Analysis in [21] compares the probability of power processed in the converters for a PV system with 10% deviation over 8 PV elements. The compared architectures are the PV-to-PV shuffling and isolated PV-to-bus architectures. Results in the analysis show that most of the power processed by the converters in the isolated architecture are below 15% of the module full power rating. On the other hand, the shuffling architecture processes power over a wide range with mean at 35%.

Viewing the results at a cost and size perspective, the shuffling architecture would likely be small due to the lower voltage rating and no need for isolation. However, the isolated case requires much less power to be processed. Hence, the size and power rating could also be reduced. However, the voltage rating of the converter would be at the PV bus voltage.

The isolated port architecture does not require the isolated bus side voltage to be at the PV bus voltage. If the architecture behaves and performs closely to the isolated PV-to-bus architecture, the converter can be design to be more efficient, smaller, and cheaper.

#### 1.4 Thesis Objectives and Organization

The dissertation goes through the design and realization of submodule integrated converters (subMICs) in the isolated-port differential power processing architecture (DPP). Designing power converters that improve PV system performance is challenged by the improvement versus cost trade-offs. It is critical for the designs to be optimized to perform not just efficiently, but also cost effectively. The DPP architecture is advantageous in reducing the cost of the converter while requiring less effort in maximizing the efficiency.

In Chapter 2, the isolated port DPP architecture is reviewed. The key advantages of the architecture are discussed, together with the control methods that can be used. The voltage balancing control scheme used in the subMICs is described.

Chapter 3 describes design details of the subMIC prototype. It includes analyzing losses in the power stage for further optimization of design. This includes planar magnetics design to optimize size and reproductivity, and control methods to improve system performance.

Chapter 4 evaluates the prototype design and verifies that it performance. Efficiency and behavior of the converters are evaluated. It also provides a deeper insight into how the controller is implemented on a custom CMOS integrated circuit (IC).

Experiment results for the DPP subMIC system are presented in Chapter 5. Experiments compare the subMIC system with the conventional system under both controlled test environment in the laboratory, and under realistic shading conditions outdoors.

Cost versus performance optimization is presented in Chapter 6. PV system installations can vary from site to site. Also, shading conditions can be very different from system to system. The presented method is developed to find the optimal design of a subMIC for different PV system installations, to maximize energy capture, while minimizing the incremental cost of subMICs.

The last Chapter summarizes the dissertation and presents possible future works.

# Chapter 2

# Isolated-port DPP Submodule Integrated Converter (subMIC)

This chapter explains the architecture, converter, and control scheme for a submodule level DPP PV system. Many configurations are possible for a DPP architecture, but few specific ones are discussed in this chapter. First, the isolated-port DPP architecture is described. Then, the DPP operation using a bi-directional flyback converter operating in discontinuous conduction mode (DCM) is explained.

#### 2.1 Architectures and Control Schemes

First, the optimal power processing method for isolated PV-to-bus architecture shown in Figure 1.8 and [18] is explained. Then, it is followed by other sub-optimal approaches and architectures.

#### 2.1.1 Optimal Control

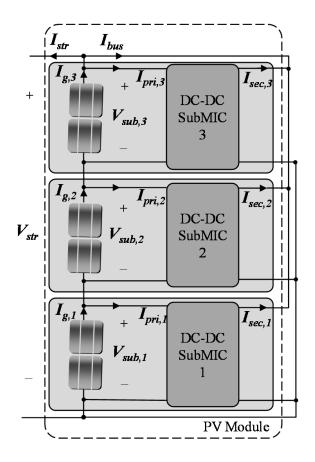

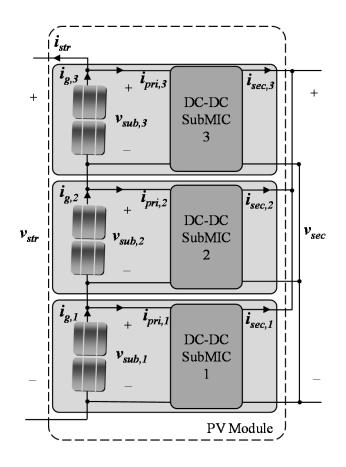

Figure 2.1 shows a single PV module with three subMICs forming the isolated PV-tobus architecture. The subMICs are isolated bi-directional DC-DC converters. It is assumed that  $V_{str}$  is controlled to be at MPP by the central inverter.

Figure 2.1: Isolated PV-to-bus architecture.

If the subMICs control  $V_{sub,i}$  to operate the substring at MPP,  $I_{g,i}$  can be determined. Then, the following linear equations can be solved to find the bus current  $(I_{bus})$  and string current  $(I_{str})$ .

$$I_{pri,2} - I_{pri,1} = I_{g,2} - I_{g,1}$$

$$I_{pri,3} - I_{pri,2} = I_{g,3} - I_{g,2}$$

$$\vdots$$

$$I_{pri,n} = I_{str} + I_{bus} - I_{g,n}$$

(2.1)

The set of equations in 2.1 does not have a single solution due to many possible  $I_{bus}$ . Optimally, a solution with minimal power processed through the subMIC would be desired. A

minimal power processed case can be found among the solutions:

$$P_{subMICs,min} = min\left\{\sum_{i=1}^{n} V_{sub,i} \mid I_{pri,i} \mid \right\}$$

(2.2)

This is the optimal power processed by the isolated PV-to-bus architecture.

Although the optimal control method provides maximum performance, it has a disadvantage in the perspective of implementation. A centralized controller is required to communicate with all subMICs to ensure minimum processed power. PV system structure varies with each installment. The central controller would have to be flexible and adaptive to be fit for all PV system structures without increasing complexity.

#### 2.1.2 Sub-optimal Control

A distributed control method not requiring central control is discussed in this section [1]. Potentially, the method enables a DPP system that is flexible to any module arrangements in a PV system. However, the power processed would not be optimal, hence it is called sub-optimal.

First, assume that all the substrings that are connected to the subMICs have matching characteristics. Then, it can further be assumed that the maximum power point voltage of the substrings  $(V_{MPP})$  are close in value. Also assume  $V_{str}$  is fixed at the string level MPP voltage  $(V_{MPP,PV})$ . If all substrings are operating at MPP, let  $I_{str}$  be the average of the substring currents.

$$I_{str} = \frac{\sum_{i=1}^{n} I_{g,i}}{n} \tag{2.3}$$

Then, current through the primary side  $(I_{pri})$  of the subMIC would equal to

$$I_{pri,i} = I_{str} - I_{g,i} \tag{2.4}$$

Now let a control with high finite gain (K(s)) force  $v_{sub,i}$  to match  $V_{MPP}$ , determining  $i_{pri,i}$ .

$$i_{pri,i} = K(s)(V_{MPP} - v_{sub,i}) \tag{2.5}$$

The total power processed in the subMICs can be found from:

$$P_{subMICs} = V_{MPP} \sum_{i=1}^{n} |I_{str} - I_{g,i}|$$

$$(2.6)$$

Comparing the power processed in the subMICs between the optimal and sub-optimal control, the sub-optimal control at the worst case, can process two times more power. This is the case where mismatched substrings generate zero power [1]. In typical mismatch scenarios, the power processed would not be so different between the two control methods.

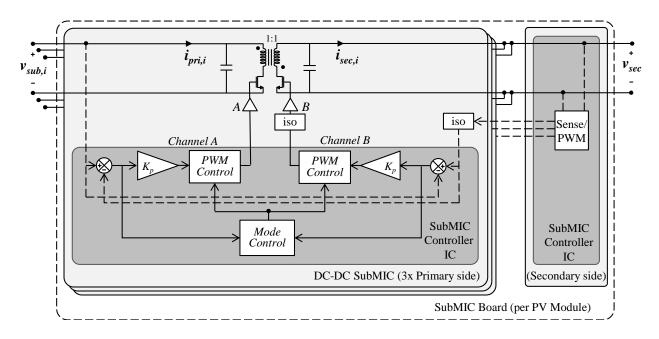

In the sub-optimal approach,  $I_{str}$  is the average of the substring currents. This is shown in equation 2.3. Then, all current processed in the isolated bus  $(I_{bus})$  is zero. Hence, the isolated bus can be removed from the PV bus. The isolated-port PV-to-bus architecture in [1] uses this as an advantage for the sub-optimal control. Now the isolated bus voltage does not have to be at the high PV bus voltage. The isolated-port PV-to-bus architecture is shown in Figure 2.2.

Figure 2.2: Isolated port PV-to-bus architecture with the auxiliary bus isolated with its voltage independent of the PV bus.

#### 2.1.3 Voltage Balancing Control

In Section 2.1.2, the sub-optimal control method was explained. Also, it shows that the auxiliary bus for power balancing does not need to be connected to the high voltage PV bus.

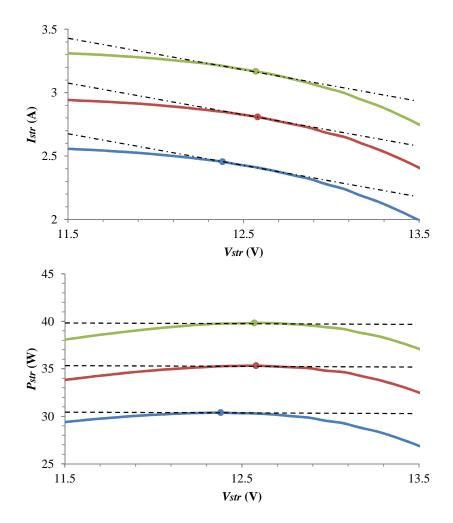

Although the net power in and out from the isolated bus would be zero, the voltage of the bus  $(V_{sec})$  is not determined. If we assume the voltage is also equal to  $V_{MPP}$ , then  $I_{pri} = I_{sec}$  would be also true. Furthermore, by observing where  $V_{MPP}$  is in the IV curve of a PV substring, the current to voltage slope around the actual  $V_{MPP}$  does not vary much with power variations. This is shown in Figure 2.3. Also, the power variations versus voltage is

small near the  $V_{MPP}$  point. Given that the subMICs will operate with  $V_{sub,i} \approx V_{MPP}$ , the

Figure 2.3: IV (top) and PV (bottom) curve of PV substrings with 25% power variations showing identical tangent lines (dot-dash, dot) overlaid over the  $V_{MPP}$  point.

string current and string voltage can be seen to be linear and inversely proportional. Then, assuming the subMICs have a 1:1 voltage conversion ratio for the isolation transformer, we can define the following control law which is dependent on the difference of subMIC port voltages, where K(s) is of finite gain.

$$i_{pri,i} = K(s)(v_{pri,i} - v_{sec}) \tag{2.7}$$

### 2.2 Voltage Balancing with Bi-directional Flybacks in DCM

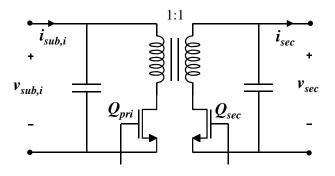

The flyback converter is a buck-boost type converter with isolation due to the flyback transformer present in the topology. It is easily modified to be a bi-directional converter as shown in Figure 2.4.

Figure 2.4: Bi-directional flyback topology used for the subMIC power stage with MOSFET switches.

The topology uses only two semiconductor switches and a single magnetic component, which makes it attractive as a cost effective solution. The drawbacks of the topology is that the semiconductor is exposed to high voltages during switching off transition. Also, the flyback transformer is designed as an energy storage device which only delivers energy at one of the switching phase.

If the flyback is operated in discontinuous conduction mode (DCM), the input can be seen as a lossless resistor and the output of the converter can be seen as a power source [22] in a large signal averaged model. With reference to the topology shown in Figure 2.4, when  $Q_{pri}$  MOSFET is on, the current on the primary inductance  $(L_{pri})$  is ramped up. When the MOSFET is turned off, the current ramps down while the body diode of  $Q_{sec}$  MOSFET conducts the current until it reaches zero. Duty cycle  $d_{pri}$  is defined as the duty ratio that the MOSFET is on for a given switching period  $(T_s)$ . Then, the lossless resistance  $(R_e)$  and the input current  $(i_{pri})$  are of the following:

$$R_e = \frac{2L_{pri}}{d_{pri}^2 T_s} \tag{2.8}$$

$$i_{pri} = \frac{v_{sub}}{2L_{pri}} d_{pri}^2 T_s \tag{2.9}$$

Extending the analysis to a bi-directional perspective, the duty cycle to current relationship can be obtained.

$$i_{pri} = v_{sub} \frac{T_s}{2L_{pri}} d_{pri}^2$$

$$i_{sec} = -v_{sec} \frac{T_s}{2L_{pri}} d_{sec}^2$$

$$(2.10)$$

Current is proportional to the square of the duty cycle. If the duty cycles were to be controlled with the port voltage difference as in equation 2.7, the port currents would be proportional to the square of the port voltage difference. Given the assumption of linearized and constant current to voltage relationship from Section 2.1.3, the following control scheme for the bi-directional flyback can be expected to achieve sub-optimal DPP performance when  $v_{sub}$  and  $v_{sec}$  are very close.

$$d_{pri} = K_p(s)(v_{sub} - v_{sec}) , when v_{sub} > v_{sec}$$

$$d_{sec} = K_p(s)(v_{sec} - v_{sub}) , when v_{sub} < v_{sec}$$

(2.11)

Gain  $K_p(s)$  is important in this control scheme. However, it does not impact system performance significantly as long as  $K_p(s)$  is sufficiently high [23].

# Chapter 3

# **Design Realization of SubMICs**

In this chapter, realizing the design of the bi-directional flyback subMICs is discussed. In a DPP system , the efficiency of the converter has less impact on the PV system efficiency than the full power processing methods. However, efficiency is still important and the converters must be designed with weight on low power efficiencies. At the same time, the converter size and cost must be minimized for PV applications.

First, the flyback power stage is discussed. Then the design and loss evaluation of planar transformer is presented. Next, the custom controller IC design and features implemented to improve efficiency are discussed. Finally, the prototype board is presented.

## 3.1 Power Stage

The power stage selected for the subMIC is a bi-directional flyback operating in DCM. Some of the critical design specifications are shown in Table 3.1.

| Maximum port voltages     | : | 16 V  |

|---------------------------|---|-------|

| Maximum port current      | : | 3 A   |

| Minimum control bandwidth | : | 1 kHz |

Table 3.1: Design specifications

Other than the electrical specifications, the converter would be required to fit in a PV

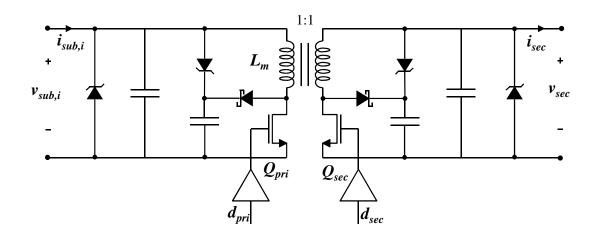

module junction box. It must be sufficiently small and thin. It should also be capable of operating at high load with sufficient efficiency while maintaining the efficiency at very low load. Low load efficiency is particularly important because the processed power distribution will be similar to a laplacian distribution weighted towards low power. Another important consideration to take into account is insertion loss. The converter and its controls should not contribute to power loss when no power processing is required. Hence, minimizing the quiescent power consumption of peripheral circuits is important. The selected flyback power stage is shown in Figure 3.1.

Figure 3.1: Bi-directional flyback topology with snubbers for a subMIC.

The converter transformer winding ratio is 1:1, keeping  $v_{sub}$  and  $v_{sec}$  at the same voltage scale. Ports are protected with zener diodes to ensure the port voltages do not exceed 18 V. The MOSFETs are exposed to at least two times the maximum port voltage, 32 V. The voltage can rise higher due to voltage spikes during turn off. Zener type snubbers are used to ensure that the MOSFETs are not exposed to excessive voltages while minimizing light load efficiency drops. The Zener voltage is set to be lower than the MOSFET rating, and higher than 32 V. MOSFETs are rated to be at 80 V. The PWM switching frequency is 100 kHz.

## 3.2 Loss Modeling

Loss estimation method for the subMIC design is presented. The losses are categorized by the dependency on switching frequency and the inductor. Typically, the DCM flyback losses can be divided into the following losses shown in Table 3.2.

| Conduction losses : | $P_{Ron}$ : MOSFET conduction loss when switch is on<br>$P_{diode}$ : MOSFET conduction loss when body diode cond |                                               |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|

|                     | 5                                                                                                                 | Gate charge loss                              |  |

| Switching losses :  |                                                                                                                   | Switching loss due to switch node capacitance |  |

|                     | $P_{leak}$ :                                                                                                      | Switching loss due to leakage inductance      |  |

|                     | $P_{Ldc}$ :                                                                                                       | Inductor DC copper loss                       |  |

| Magnetic losses :   | $P_{Lac}$ :                                                                                                       | Inductor AC copper loss                       |  |

|                     | $P_{core}$ :                                                                                                      | Core loss                                     |  |

Table 3.2: Loss type classification for the DCM flyback

Since the converter is symmetric, loss modeling is explained with power flowing from the primary side to the secondary side of the converter.

#### 3.2.1 Conduction Loss

The DCM flyback operates with zero current at the beginning of a switching period  $(T_s)$ . When the primary side  $Q_{pri}$  is turned on, the current through the MOSFET is ramped up until the switch is turned off, forming a triangular waveform with a peak current  $(I_{pk})$ . The duration of this phase is  $D_1T_s$ . Then, the current is conducted on the other side of the winding through the body diode of  $Q_{sec}$ . The current ramps down from  $I_{PK}$  to zero in  $D_2T_s$ . The conduction losses can be defined as the following:

$$P_{cond} = I_{pk}^2 \frac{D_1}{3} \cdot R_{on} \tag{3.1}$$

$$P_{diode} = I_{pk} \sqrt{\frac{D_2}{3}} \cdot V_{sec} \tag{3.2}$$

where,

$$I_{pk} = \frac{V_{pri}}{L} D_1 T_s \tag{3.3}$$

$$D_2 = I_{pk} \frac{L}{V_{sec} T_s} \tag{3.4}$$

#### 3.2.2 Switching Loss

Gate charge related loss is from the gate charge required to turn on the MOSFET. This energy is lost when the MOSFET is turned off. Given the gate charge of the MOSFET  $(Q_g)$  at a given driving voltage  $V_{gate}$ . The gate drivers loss can be estimated by Equation 3.5. The power loss associated from the gate driver power supply and the circuits associated with the drivers are neglects.

$$P_{gate} = Q_g \cdot V_{gate} \cdot f_s \tag{3.5}$$

Switch node capacitance loss is also related to the MOSFET device and parasitic capacitances. If the capacitances seen at the drain of the MOSFET are lumped together as  $C_{oss}$ , the loss can be estimated as in Equation 3.6.

$$P_{coss} = \frac{1}{2} C_{oss} (V_{pri} + V_{sec})^2 \cdot f_s$$

(3.6)

Assume the MOSFET turn off speed is much faster than the ramp of the leakage inductance  $(L_{lk})$  current to zero. Then, it can be assumed that the leakage current  $(i_{lk})$  is all dissipated through the zener clamping diode in the snubber. The power loss can be calculated as Equation 3.7.

$$P_{leak} = \frac{1}{2} I_{pk} V_{zener} \cdot T_x \cdot f_s \tag{3.7}$$

where  $T_x$  is the time that it takes for  $i_{lk}$  to ramp down from  $I_{pk}$  to zero.

$$T_x = I_{pk} \frac{L_{lk}}{V_{zener} - V_{sec}} \tag{3.8}$$

#### 3.2.3 Magnetics Loss

The flyback transformer consists of multiple windings which transfers power over one winding to another. It acts more like an inductor. The stored energy is transfered between the windings. In a DCM flyback, only one winding conducts current at a given time. When  $Q_{pri}$  is on, the current flows through the primary side winding. When it is turned off, current flows through the secondary side winding, until the current reaches zero.

If  $R_{Ldc,pri}$  is the primary side winding resistance and  $R_{Ldc,sec}$  is the secondary side winding resistance, the DC copper loss of the magnetic component can be estimated similarly as the MOSFET conduction loss since the winding currents are equal to the MOSFET currents.

$$P_{Ldc,pri} = I_{pk}^2 \frac{D_1}{3} \cdot R_{Ldc,pri}$$

$$(3.9)$$

$$P_{Ldc,sec} = I_{pk}^2 \frac{D_2}{3} \cdot R_{Ldc,sec}$$

$$(3.10)$$

where  $I_{pk}$  and  $D_2$  are found in Equation 3.3 and 3.4.

The AC portion of the current generates fields around the copper, contributing to other conduction losses. These losses can be classified into eddy current loss, winding proximity loss, and airgap fringing flux related losses. Much work are done in estimating these losses, but the loss calculation is relatively complex and must consider the underlying assumptions made in the calculations [22,24–26]. Proximity loss considering frequency decomposition for the flyback transformers have been investigate in [27,28]. Studies in [29,30] show how AC copper loss due to airgap fringing can be estimated and also suggests what is required to minimize the losses.

Instead of using the methods used in the literatures, 2-D finite element method simulation, FEMM [31], is used to estimate the AC related copper losses. A cross-section of the flyback transformer is analyzed through frequency decomposition. Then the equivalent AC resistance for each decomposed frequency component is found. Next, the AC copper resistance is extrapolated to the mean length turn (MLT) of the winding. Finally, loss is summed up as the following.

$$P_{Lac,pri} = \sum_{n=1}^{harm} I_{pk,n\cdot f}^2 R_{Lac,pri,n\cdot f}$$

(3.11)

$$P_{Lac,sec} = \sum_{n=1}^{harm} I_{pk,n\cdot f}^2 R_{Lac,pri,n\cdot f}$$

(3.12)

The core loss can be estimated using the piecewise waveform analysis using Steinmetz parameters [32]: the improved Generalized Steinmetz Equation (iGSE). This method uses the usual Steinmetz parameters for a material:

- $K_{fe}$  : core loss coefficient

- $\alpha$  : frequency exponent

- $\beta$  : density flux exponent

The Steinmetz model is known to be a good choice for modeling core loss. However, it assumes the signal is a sinusoidal waveform. The iGSE method includes the high frequency component of the waveform for improved accuracy. Core loss is calculated as Equation 3.13.

$$P_{core} = \frac{1}{T_s} \int_0^{T_s} k_i \left| \frac{dB}{dt} \right|^a (\Delta B)^{\beta - \alpha} dt$$

(3.13)

where

$$k_i = \frac{K_{fe}}{(2\pi)^{\alpha-1} \int_0^{2\pi} |\cos\theta|^{\alpha} 2^{\beta-\alpha} d\theta}$$

(3.14)

However, this method does not consider affects from DC bias.

## **3.3** Planar Magnetics

The magnetic component is the largest component in the subMIC. It determines the overall height of the subMIC. Planar magnetic design on PCB allows the windings to be of lower height. Also the windings can be reproduced to be close to identical. Another advantage is that the core can be place right on the PCB. However, the planar multilayer winding has some disadvantages. First, the planar windings stacked up in planes form nice capacitive plates. The capacitance can degrade inductive performance and also allow high frequency current across the transformer isolation.

Few selected set of designs are produced to compare the actual performance of the magnetics to the loss models. Designs are selected based on the optimal design selection based on the loss estimates. Core selection and winding configurations are varied in the set. Target inductance for the power stage is 7-8  $\mu$ H, switching frequency is 100 kHz, and the peak current in the magnetic is expected to be safe at 10 A.

In this section, candidate magnetic designs are selected for loss estimation. Then, optimal designs are manufactured as final candidates for the subMICs.

#### 3.3.1 Core Selections

Through rough analysis, a family of ferrite cores from TDK are selected. The selected material for the core is the PC95 material, which has stable loss characteristics versus temperature. The core loss is expected to be relatively low for this material. Saturation flux density is 410 mT at 100 C, and the loss density is estimated to be 300 kW/m<sup>3</sup> at 200 mT and 100 kHz. Flat ELT type cores that are specific to PCB planar design are selected. For comparison of size, a POT type core is shown with ELT core candidates in Figure 3.2. The specifications of the selected ELT cores are shown in Table 3.3.

Given the maximum operating point and specifications for the power stage, the peak flux densities are evaluated in Table 3.4. The results show that minimum of 4 turns will keep the core out of saturation range for 20 and 22 size cores. For further evaluation, cores size 20 and 22 are considered. Also, turns of 4 or more are considered.

The cores will have an airgap at the junction of the E and I shaped core. The core comes in two winding heights: 2 mm and 4 mm.

Multiple layer PCBs will be used for the windings. If the overall height of the planar

Figure 3.2: TDK ELT type cores for the design and a POT core.

|                 | $A_e$ (mm <sup>2</sup> ) | $l_e(\text{mm})$ | $A_L(nH/N^2)$ |

|-----------------|--------------------------|------------------|---------------|

| PC95ELT18X7.3-Z | 44.3                     | 23.8             | 4760          |

| PC95ELT20X5.7-Z | 54.9                     | 21.6             | 6270          |

| PC95ELT20X7.7-Z | 54.6                     | 25.6             | 5630          |

| PC95ELT22X6-Z   | 66.6                     | 23.4             | 7250          |

| PC95ELT22X8-Z   | 66.2                     | 27.3             | 6540          |

Table 3.3: Specifications for TDK ELT type cores. Effective core area  $A_e$ , length  $l_e$ , and the inductance per wind estimation factor  $A_L$  is shown.

| Bmax(mT)        | Turns |     |     |     |     |     |

|-----------------|-------|-----|-----|-----|-----|-----|

|                 | 3     | 4   | 5   | 6   | 7   | 8   |

| PC95ELT18X7.3-Z | 602   | 452 | 361 | 301 | 258 | 226 |

| PC95ELT20X5.7-Z | 486   | 364 | 291 | 243 | 208 | 182 |

| PC95ELT20X7.7-Z | 488   | 366 | 293 | 244 | 209 | 183 |

| PC95ELT22X6-Z   | 400   | 300 | 240 | 200 | 172 | 150 |

| PC95ELT22X8-Z   | 403   | 302 | 242 | 201 | 173 | 151 |

Assume fs=100kHz, Ipk=10A, L=8uH

Table 3.4: Worst case flux density for the cores are given for several candidate turns. Green denotes flux density is below 70% of saturation and red denotes that the core would saturate.

winding is too thin, parasitic capacitance increases. If the height increases, the windings become closer to the airgap.

According to [26], the loss due to airgap fringing flux is dependent on the airgap length and distance between the airgap, versus the copper distance from the airgap. It is found in later sections that the copper windings should be more than 2 mm away from the airgap to minimize airgap related loss. Considering the thickness of high ounce copper and insulation material between the copper, it is difficult to use the 2 mm height window for multiple layer PCB with high ounce copper. The 4 mm height window provides more flexibility in design with the trade off of larger core volume. The 4 mm height cores are considered for the designs. This corresponds to the ELT20x7.7 and ELT22x8 cores.

#### 3.3.2 Winding Selections

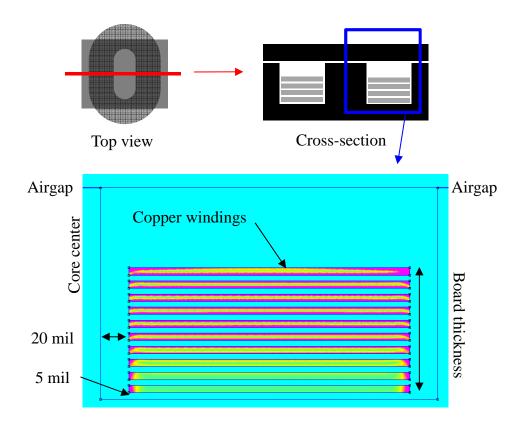

Winding of the magnetics are designed on the copper layers of a PCB. The design can have multiple turns of winding on a single PCB layer or have multiple PCB layers for multiple turns. Due to the small geometry of the core, single turn per PCB layer is used for the prototype design. Even a two turn per layer winding would be hard to design due to the vias required near the center of the winding. It would only be possible to fit one or two minimal sized vias. The winding structure relative to the core are shown in Figure 3.3.

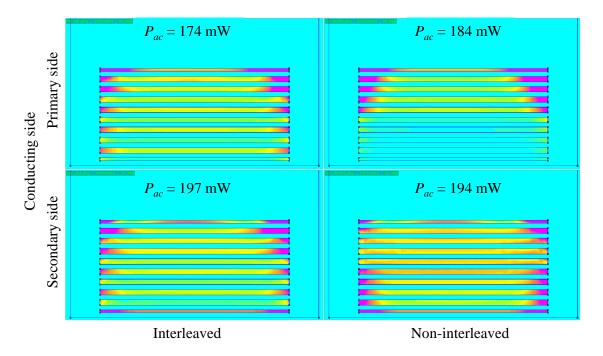

From the winding configuration chosen, whether to interleave the winding layers or not can be decided. In transformers, wire interleaving is used to minimize proximity losses. The opposing current direction of each transformer winding mitigates the MMF build between the windings. The trade-off of this is the increase of parasitic inter-winding capacitance. In the DCM flyback, only one of the windings conduct current at a given time. The benefit of interleaving would be weak. Performance analysis of interleaving is done in FEMM using the 2-D cross-section of the magnetics. The analysis compares the AC copper loss of a 5 turns per winding case. Loss is evaluated for a 4 A peak sinusoidal at 100 kHz. The stack is designed with the secondary side winding on the bottom most side closest to the core, then stacked up. Both primary and secondary side excitation is compared. Loss evaluated is the sum of both winding losses for a given scenario. FEMM results are shown in Figure 3.4.

Figure 3.3: Diagram of core and winding structure with key design geometries shown.

Results show that interleaving does not improve AC related loss significantly. It also shows that it could worsen the loss very slightly in the secondary side conduction phase. The benefit from interleaving the windings is small while the complexity of designing the PCB would increase. The analysis suggests that the copper winding location is more relevant to loss than whether or not interleaving is used. Therefore, interleaved winding is not considered in the design.

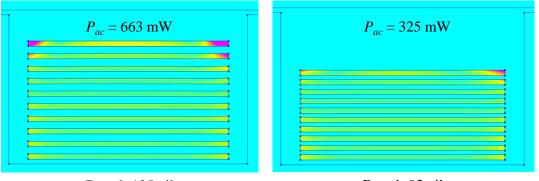

Next, the board thickness is determined. For the design, only turns of 4 or more are considered for the winding designs. Given that 5 turns per winding is chosen with 4 oz copper, the minimum board thickness possible would be of 93 mil. FEMM analysis is performed for 93 mil and 125 mil board thicknesses to analyze loss increase related to the airgap. The 125 mil case has the minimum distance from the airgap reduce by half compared to the 93 mil

Figure 3.4: FEMM analysis results comparing interleaved (left column) and non-interleaved (right column) AC copper loss when excited with a 4 A, 100 kHz sinusoidal current in the primary side winding (top row) and secondary side (bottom row). Magenta indicates higher current densities and cyan indicates the lowest current densities.

board. For the analysis, the secondary side winding on the bottom side is excited with a 4 A peak sinusoidal at 100 kHz. Figure 3.5 shows the results. Loss is evaluated in the same manner as the analysis done for the interleaved winding case.

Results show that the AC copper loss doubles for the 125 mil board. Considering that there is proximity and eddy current losses already present in the total loss, loss contribution from the airgap fringing flux is very significant. Visually analyzing the results, increase in current density due to the airgap is already observed in the top corners of the 93 mil thick board. Therefore, only copper ounces below 4 oz and 5 turns are considered for the design.

#### 3.3.3 Loss Estimations

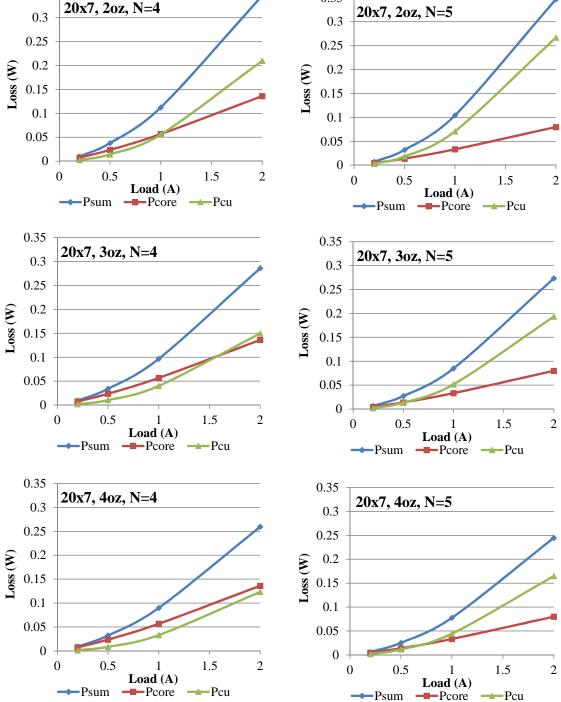

Loss evaluation are performed for selected design sets considered in the previous section. Loss estimates are evaluated for the combination of following design variations:

Board=125mil

Figure 3.5: FEMM analysis results comparing AC loss dependent on the distance from the airgaps while the bottom winding is excited with current.

- Cores : ELT20x7 and ELT22x8 cores with PC95 material

- Copper ounce : 2, 3, and 4 oz copper

- Winding turns : 4 and 5 turns per winding